【Cadence32】PCB多层板电源、地平面层创建心得➕CM约束管理器Analyze分析显示设置➕“DP”报错DRC

【转载】Cadence Design Entry HDL 使用教程

【Cadence01】Cadence PCB Edit相对延迟与绝对延迟的显示问题

【Cadence02】Allegro引脚焊盘Pin设置为透明

【Cadence03】cadence不小心删掉钢网层怎么办?

【Cadence04】一般情况下Allegro PCB设计时的约束规则设置(自己瞎写)

【Cadence06】cadence HDL原理图库添加封装

【Cadence09】Cadence PCB布线时的电源地操作

【Cadence12】总结--多层板PCB绘制、丝印调整以及生成GND

【Cadence13】Cadence HDL导出BOM并将网页数据导入Excle➕坐标文件

【Cadence14】Cadence HDL原理图创建时多个VCC或GND处理方法

【Cadence15】Cadence HDL原理图打印➕allegro打印装配层丝印的技巧

【Cadence16】Cadence HDL如何拷贝模版项目?

【Cadence19】如何由PCB导出symbol器件PCB封装

【Cadence22】将别人发的原理图和PCB库修改为自己的库,进而继续制图

【Cadence23】Cadence HDL原理图如何将两个不同的全局网络连接

【Cadence25】异形板框由DXF直接导入allegro

【Cadence27】HDL拷贝工程➕Allegro导出DXF和3D文件STP

【Cadence31】PCB放置器件布局和走线时栅格点Grid大小设置➕防天线效应走线

目录

1. 创建平面层

【注意Tips】

①平面层是指该层全部是铺铜,没有走任何一根走线!!!

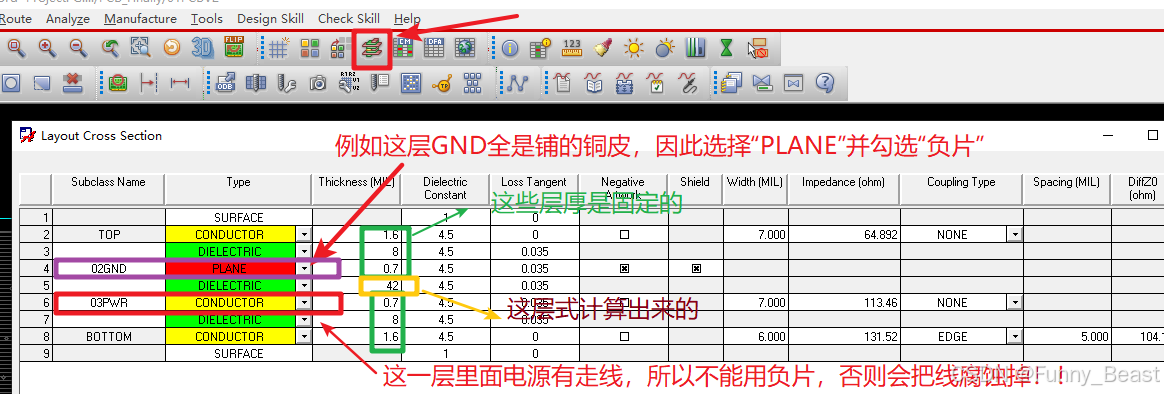

②在层叠设置中记住要设置一下!!!

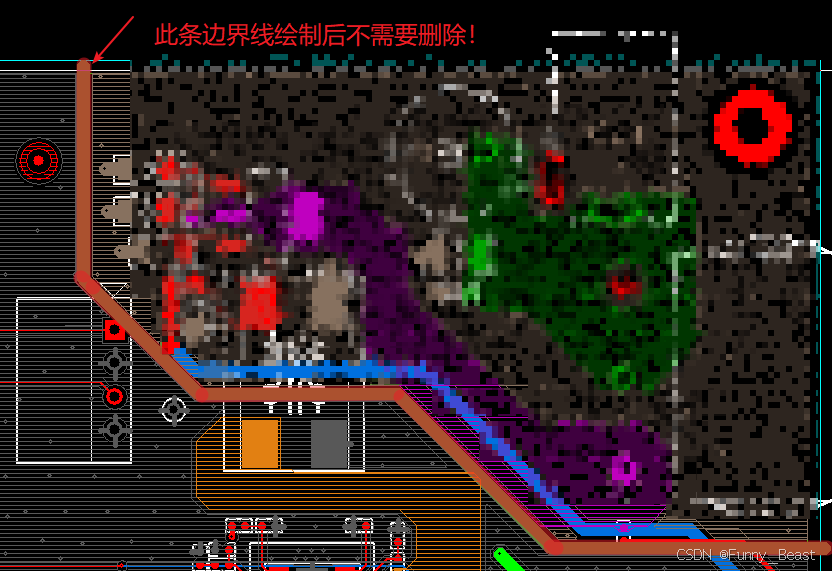

1)在平面层要先绘制边界线Line,选择Anti Etch,线宽设置为40mil即可。

![]()

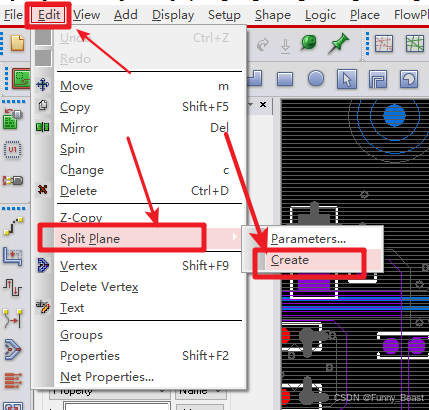

2)创建自动生成平面。

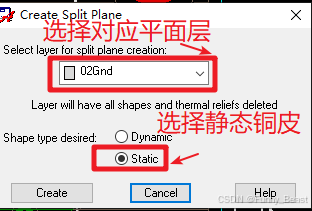

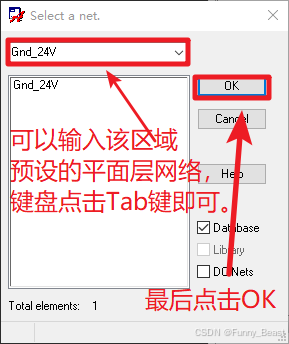

3)之后会自动高亮分割后平面层的一个区域,对该区域网络Net进行选择即可。

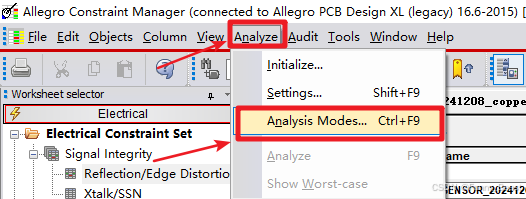

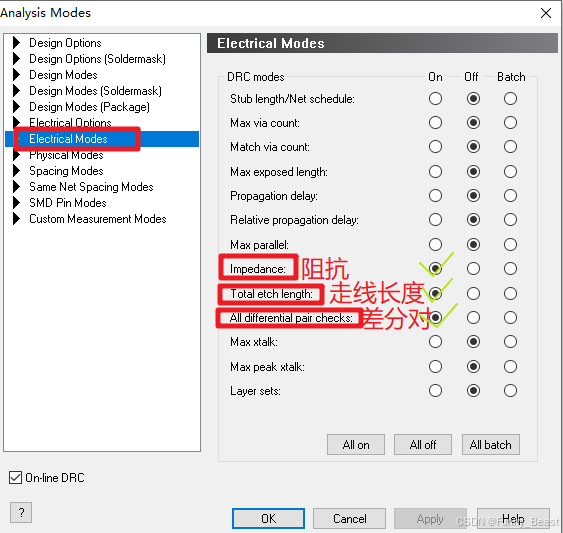

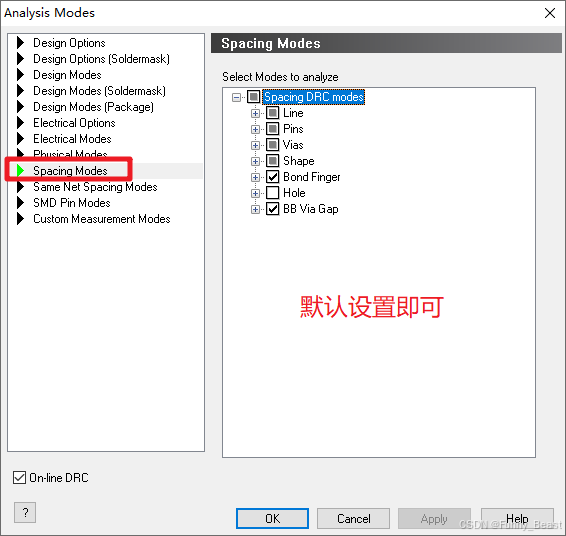

2.CM约束管理器Analyze分析显示设置

1)打开CM约束管理器

![]()

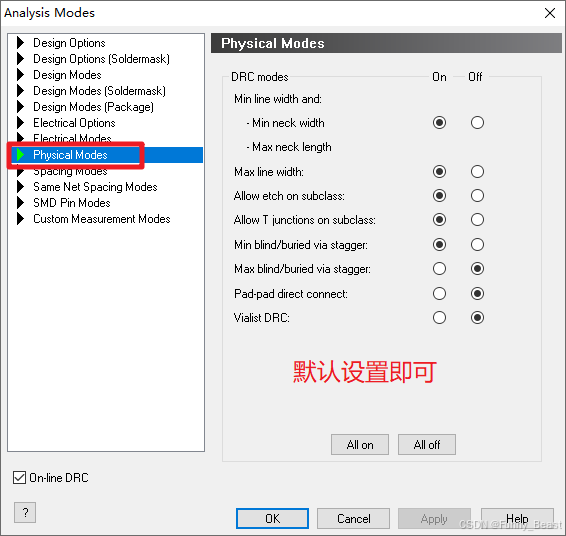

2)设置如下:

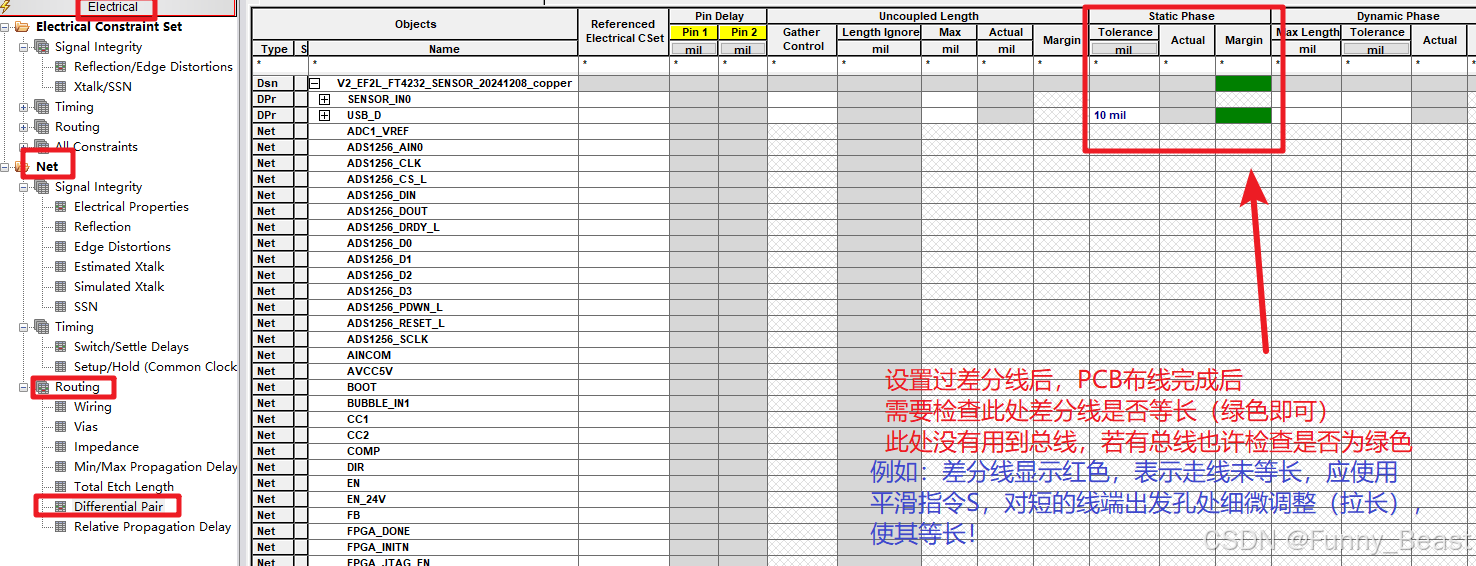

3.差分走线DRC报错“DP”

【分析】差分线出现DRC报错“DP”,两根差分线未做等长处理。

解决办法:使用平滑指令S,对差分线进行微调,短的线多弯一点,增加长度。

当差分走线为绿色时,即可。

原文地址:https://blog.csdn.net/Funny_beast/article/details/144294539

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!