数字集成电路(7)---时序逻辑电路设计

数集第六章重点

在数字电路系统中,有限状态机是一种十分重要的时序逻辑电路模块

有限状态机(FSM),它由组合逻辑和寄存器组成

有三个重要的时序参数与寄存器有关。

1.建立时间(Tsu)是在时钟翻转 (对于正沿触发寄存器为0→1的翻转)之前数据输入(D)必须有效的时间。

2.维持时间(Thold)是在时钟边沿之后数据输入必须仍然有效的时间。

3.传播延时(Tc-q)是寄存器传播延时。

假设一个逻辑最坏情形的延时等于 t p l o g i c t_{plogic} tplogic,而它的最小延时一也称为污染延时(contamination delay )为tcd。时序电路正确工作所要求的最小时钟周期T为:

T ≥ t c − q + t p l o g i c + t s u T\geq t_{c-q}+t_{plogic}+t_{su} T≥tc−q+tplogic+tsu

t c d r e g i s t e r t_{cdregister} tcdregister是寄存器的最小传播延时(或称污染延时)

t c d r e g i s t e r + t c d l o g i c ≥ t h o l d t_{cdregister}+t_{cdlogic}\geq t_{hold} tcdregister+tcdlogic≥thold

只要接通电源,静态存储器就会一直保存存储的状态。

动态存储器的数据只存储很短的一段时间,也许只有几毫秒。它们的工作原理是在与 MOS器件相关的寄生电容上暂时存储电荷。

锁存器是构成边沿触发寄存器的主要部件。它是一个电平敏感电路,即在时钟信号为高电平时把输入D传送到输出Q, 此时锁存器处于透明(transparent)模式。当时钟为低电平时,在时钟下降沿处被采样的输入数据在输出端处,整个阶段都保持稳定,此时锁存器处于维持(hold)模式。 输入必须在时钟下降沿附近的一段校短时间内稳定以满足建立时间和维持时间的要求。工作在这 些情形下的锁存器即为正锁存器。

不同于电平敏感锁存器,边沿触发的寄存器只在时钟翻转时才采样输入:0→1翻转时采样称为正沿触发寄存器,而1→0翻转时采样称为负沿触发寄存器。

一个边沿触发的存储元件称为寄存器;

锁存器是一个电平敏感的器件;

由交叉耦合的门构成的任何双稳态元件称为触发器(flip-flop )。

触发器只有在使电路从一种状态变为另一种状态时才有用。这一般可以采用如下两种方法来实现。

1.切断反馈环路 :

2.触发强度超过反馈环:

建立一个锁存器最稳妥和最常用的技术是采用传输门多路开关。

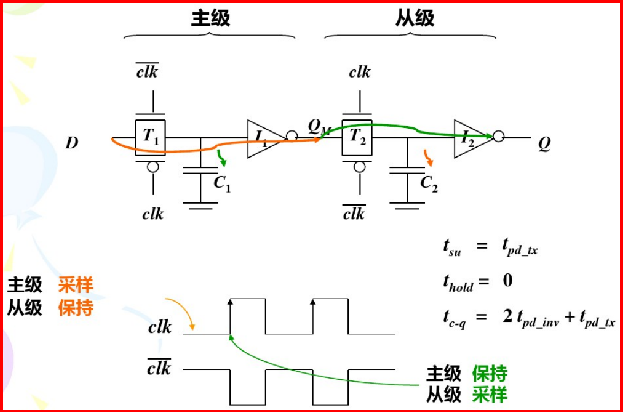

构成一个边沿触发寄存器的最普通方法是采用主从结构。

假设每一个反相器的传播延时为: t p d − i n v t_{pd-inv} tpd−inv;

传播门的传播延时: t p d − t x t_{pd-tx} tpd−tx;

污染延时为0;

时钟产生的反相器延时为0.

建立时间Tsu=3 × t p d − i n v + t p d − t x \text{建立时间Tsu=3}\times\mathrm{t_{pd-inv}+t_{pd-tx}} 建立时间Tsu=3×tpd−inv+tpd−tx

t c − q = t p d − i n v + t p d − t x \mathrm{t_{c-q}=t_{pd-inv}+t_{pd-tx}} tc−q=tpd−inv+tpd−tx

因此维持时间为0。

传输门寄存器的缺点是时钟信号的电容负载很大。

反相器中驱动能力最强的应该是?

用高阈值器件来选通低阈值器件的电源以消除漏电

锁存器正常传输信号时,用低阈值器件,锁存器维持时,用高阈值器件。

静态时序电路的存储依赖于如下概念:

一对交叉耦合的反相器形成了一个双稳元件并且因此可以用来记忆二进制值。这个方法有一个很有用的特性,即只要电源电压加在该电路上,它所保存的值就一直有效,因此称为静态电路。

这一电路的建立时间就是传输门的延时,它相应于节点C1采样D输入所需要的时间。维持时间近似为0,因为传输门在时钟边沿处关断,因此不受输入进一步变化的影响。传播延时tc-q等于两个反相器的延时加上传输门T2的延时。 对于这样一个动态寄存器,需要好好考虑的是存储节点必须周期性地刷新,以防止因电荷泄漏、二极管泄漏或亚阈值电流引起的电荷丢失。在数据通路电路中刷新的频率不是一个问题,因为寄存器受到时钟周期性的控制,所以存储节点在不断更新。

t o v e r l a p 0 − 0 < t T 1 + t I 1 + t T 2 t_{overlap0-0}<t_{T1}+t_{I1}+t_{T2} toverlap0−0<tT1+tI1+tT2

t h o l d > t o v e r l a p 1 − 1 t_{hold}>t_{overlap1-1} thold>toverlap1−1

一种对时钟偏差不敏感的方法— c 2 m o s c^2mos c2mos寄存器

流水线—优化时序电路的一种方法

t o v e r l a p 0 − 0 < t T 1 + t I 1 + t T 2 t_{overlap0-0}<t_{T1}+t_{I1}+t_{T2} toverlap0−0<tT1+tI1+tT2

t h o l d > t o v e r l a p 1 − 1 t_{hold}>t_{overlap1-1} thold>toverlap1−1

一种对时钟偏差不敏感的方法— c 2 m o s c^2mos c2mos寄存器

流水线—优化时序电路的一种方法

流水线是一种非常普遍的设计技术.经常用来加速数字处理器的数据通路。为保证正确求值,所需要的最小时钟周期为: T m i n = t c − q + t p d − l o g i c + t s u , t c − q T_{min}=t_{c-q}+t_{pd-logic}+t_{su},t_{c-q} Tmin=tc−q+tpd−logic+tsu,tc−q和 t s u t_{su} tsu分别为寄存器的传播延时和建立时间. t p d − l o g i c t_{pd-logic} tpd−logic代表通过组合电路最坏情形下的延时路径.

原文地址:https://blog.csdn.net/u011146203/article/details/140591044

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!