chisel RegInit/UInt/U

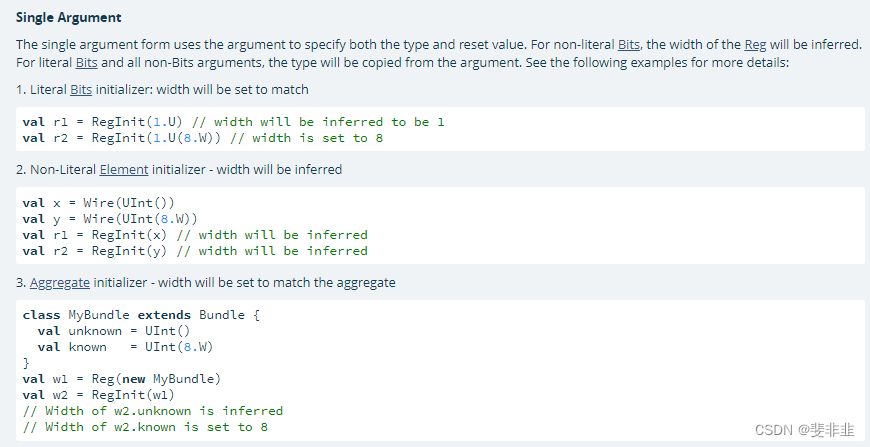

val reg = RegInit(0.U(8.W)) //ok

val reg = RegInit(0.UInt(8.W)) //err

U 使用在数字 . 后边50.U

UInt 使用在IO(new Bundle val a = Input(UInt(8.W)) 或者 def counter(max:UInt, a1:UInt)

package empty

import chisel3._

import chisel3.util._

class MyCounter extends Module {

val io = IO(new Bundle {

val a = Input(UInt(8.W))

//val a = Input(U(8.W))

val c = Output(UInt(8.W))

})

val init = io.a

def counter(max:UInt, a1:UInt) ={ //max:U //err

val reg = RegInit(a1) //ok

//val reg = RegInit(0.U(8.W)) //ok

//val reg = RegInit(0.UInt(8.W)) //err

when(reg===max) {

reg := 0.U(max.getWidth.W)

}.otherwise {

reg := reg + 1.U(1.W)

}

reg // return value

}

io.c := counter(50.U, io.a)

}

object MyCounterMain extends App {

println("Generating the adder hardware")

emitVerilog(new MyCounter(), Array("--target-dir", "generated"))

}

原文地址:https://blog.csdn.net/weixin_39060517/article/details/136024656

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!