HDL coder使用手册

💡 由于本科毕设女朋友准备使用FPGA完成,因此写这篇文章帮助她快速上手HDL coder的使用,降低前期入门的难度。

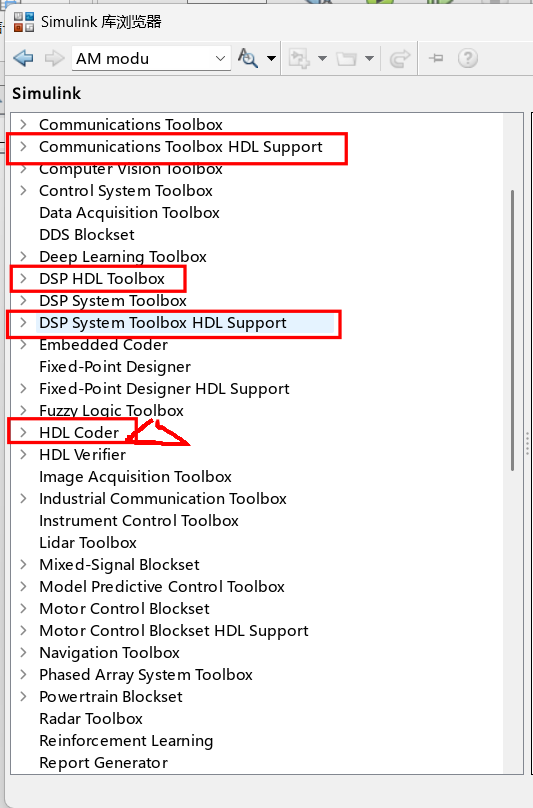

支持生成HDL代码的simulink库

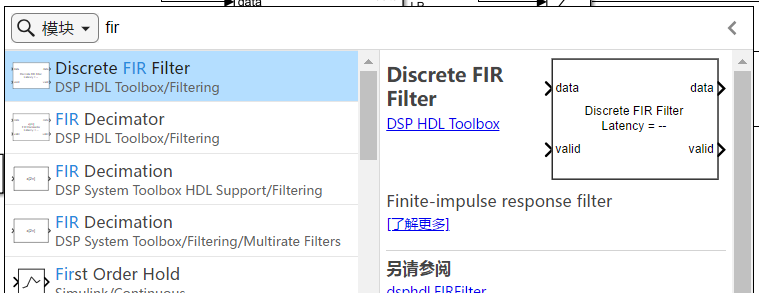

名字中含有HDL的库中的模块一般都可以用来生成HDL代码。直接搜索模块名称,比如搜索fir,

可以看到旁边会显示位于哪个库中,模块有可能位于多个库,只要有一个库的名字里面有HDL,就代表这个模块可以用来生成HDL代码。

一些常用操作

创建子系统

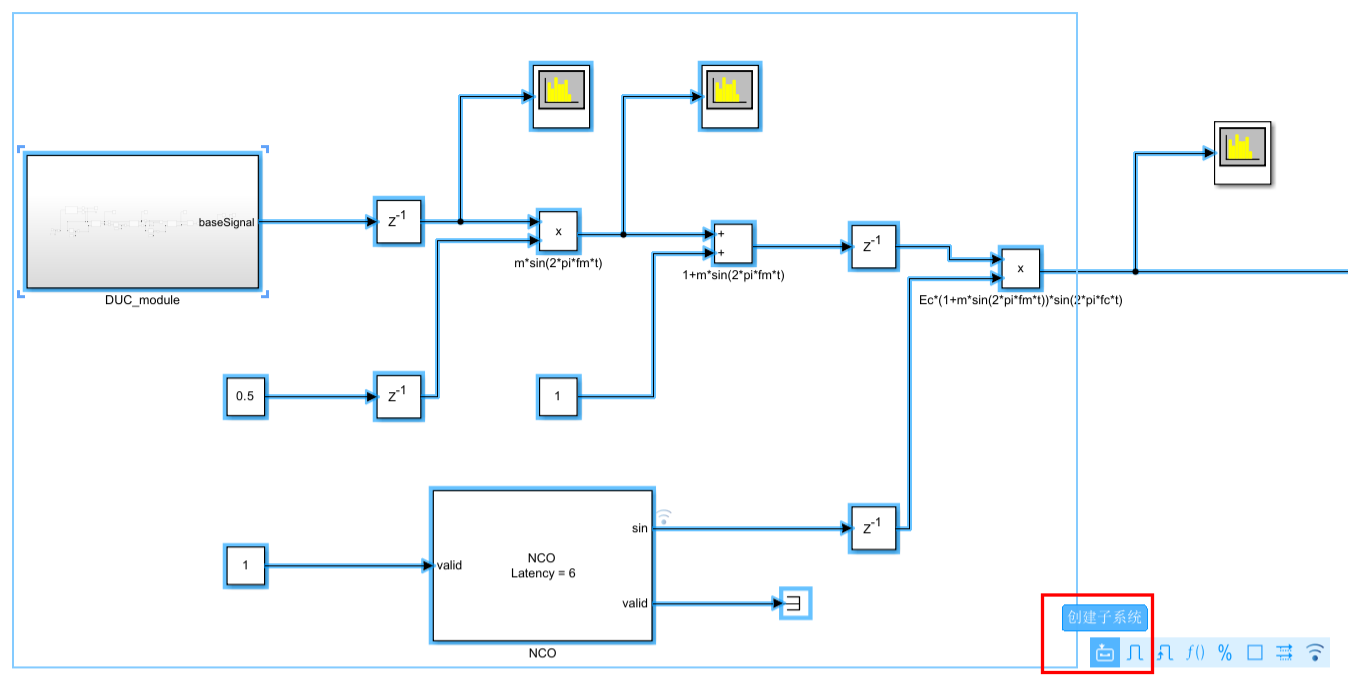

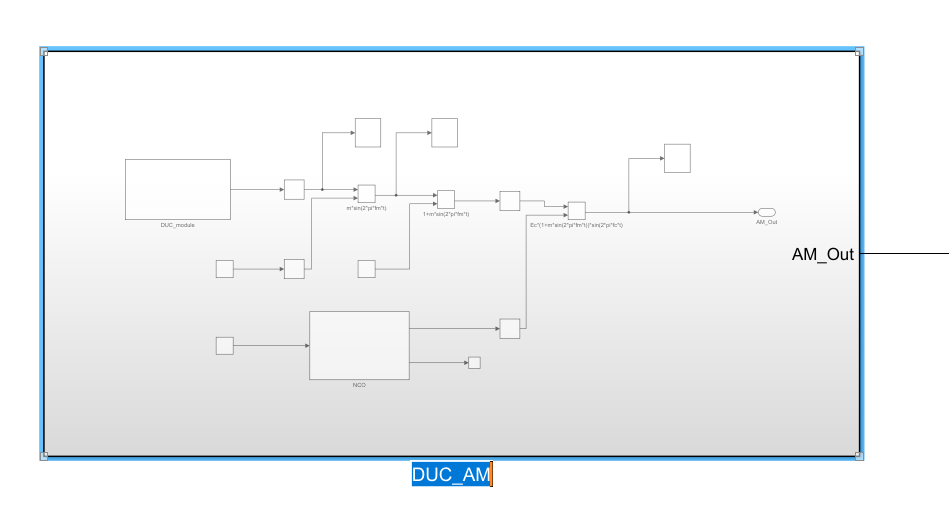

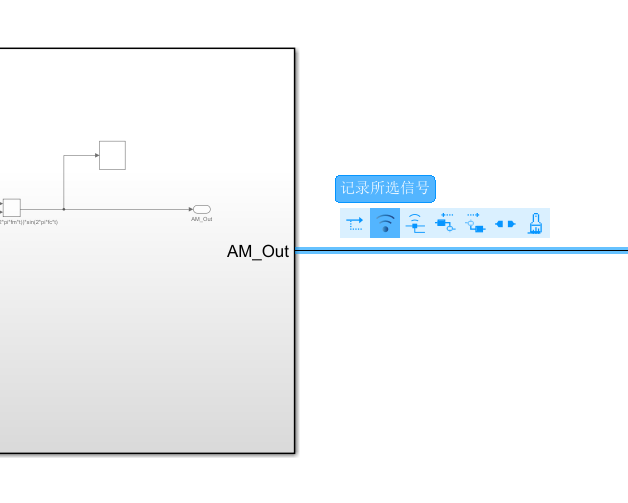

将库中的模块拖到主界面组合好后,可能会占据很大的空间,如果工程较大,模块越连越多就特别臃肿,因此当我们完成某个功能以后,就可以将这部分的模块全部选中,此时右下角会出现三个点,将鼠标移到上面后会展开,出现很多不同的功能。下图是一个AM调制的过程,可以看到选中所有相关的模块后点击创建子系统,即可得到右图的子系统。刚生成的子系统的命名为subsystem,可以将命名改为更清晰易懂的名字。

观察节点的信号波形

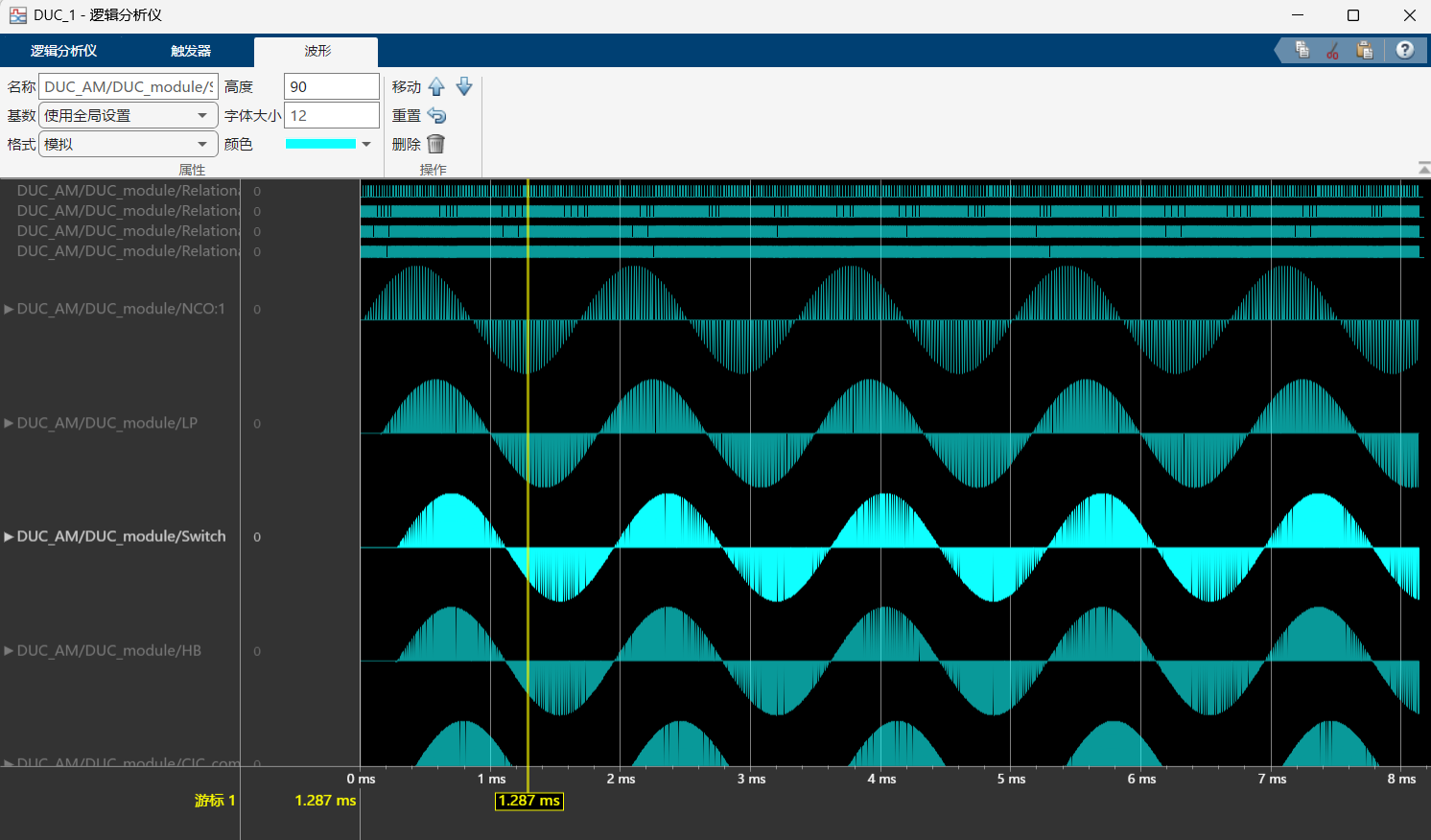

当选中某根连线时,同样会出现三个点,鼠标移动到上面后会展开,选择WiFi形状的选项即可记录该连线上的信号。运行仿真后再次点击WiFi图标即可打开逻辑分析仪,即可查看该连线上的信号。

逻辑分析仪内部选中某个信号后即可在波形中调节数制、高度等设置。

也可以使用scope模板看节点信号。

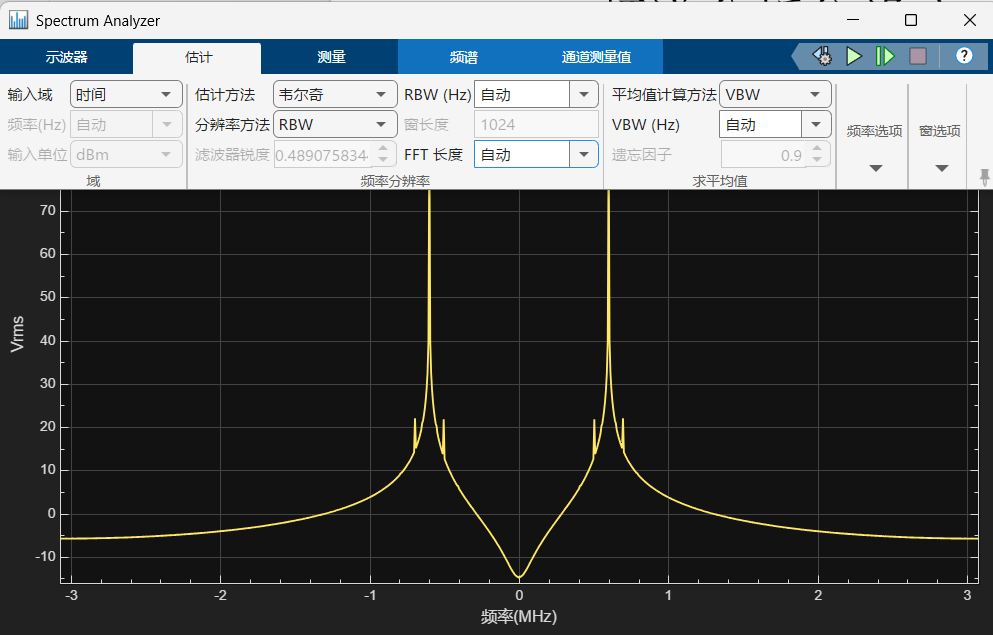

频谱分析

使用Spectrum Analyzer模块进行频谱分析。

当样点比较少的时候可以将估计方法改为welch。

信号数据格式显示

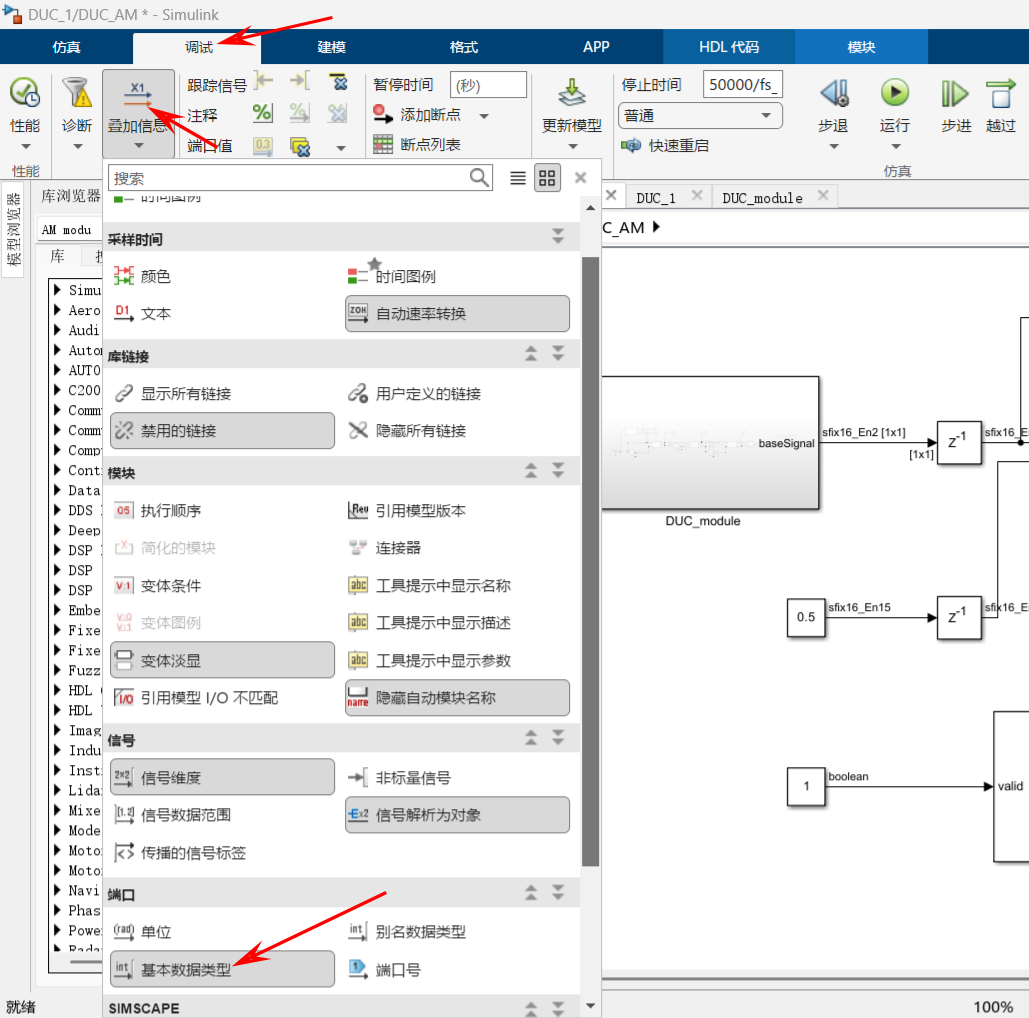

可以显示模块输入输出信号的数据类型和小数位数。

采样时间一栏中的时间图例选中以后,会用不同的颜色显示不同采样速率的模块,在多速率系统设计中有很大的用处。

生成HDL代码

前期准备

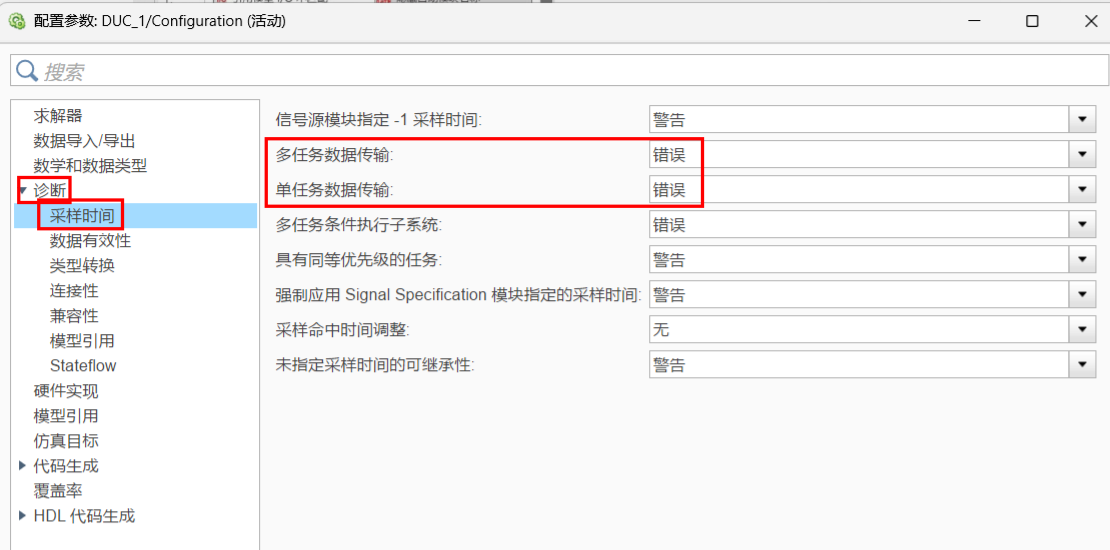

设置诊断类型

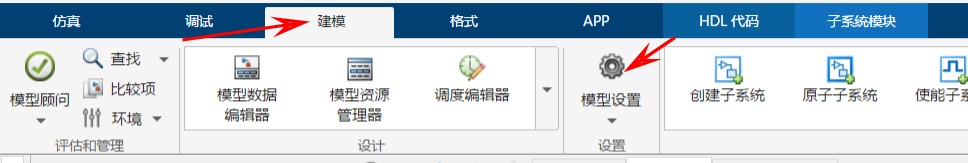

模型设置中选择诊断/采样时间

单任务和多任务数据传输必须设置成错误。

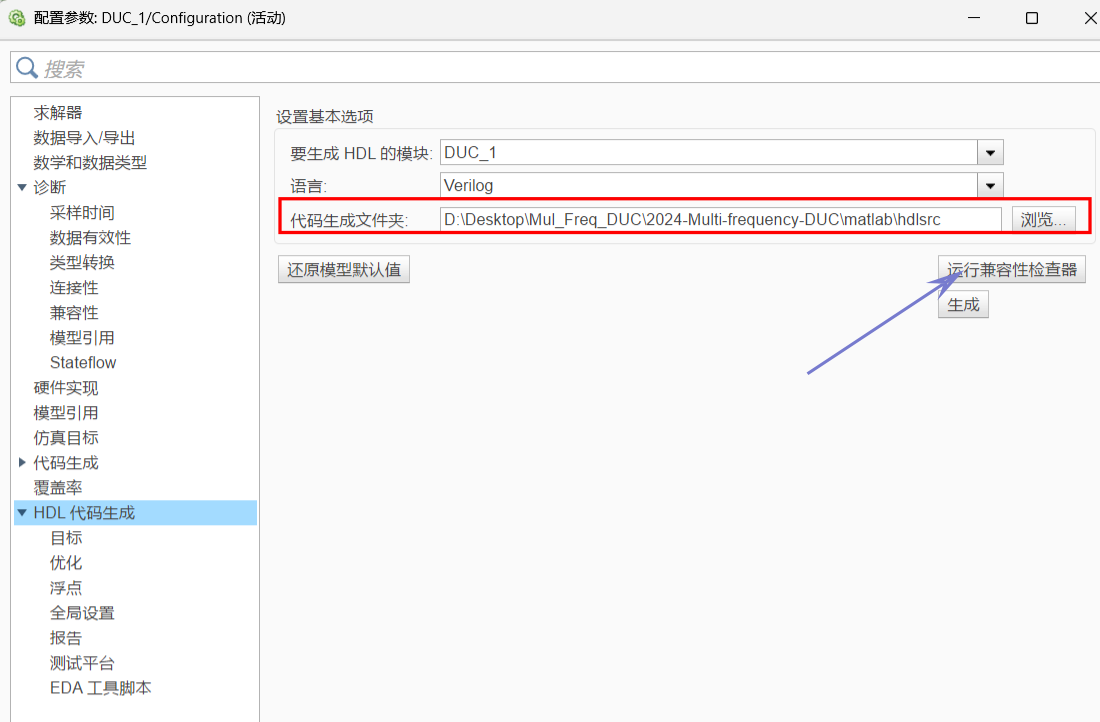

兼容性检测

选择代码生成的目标文件夹,运行兼容性检查器,如果工程没有问题的话会出现如下界面

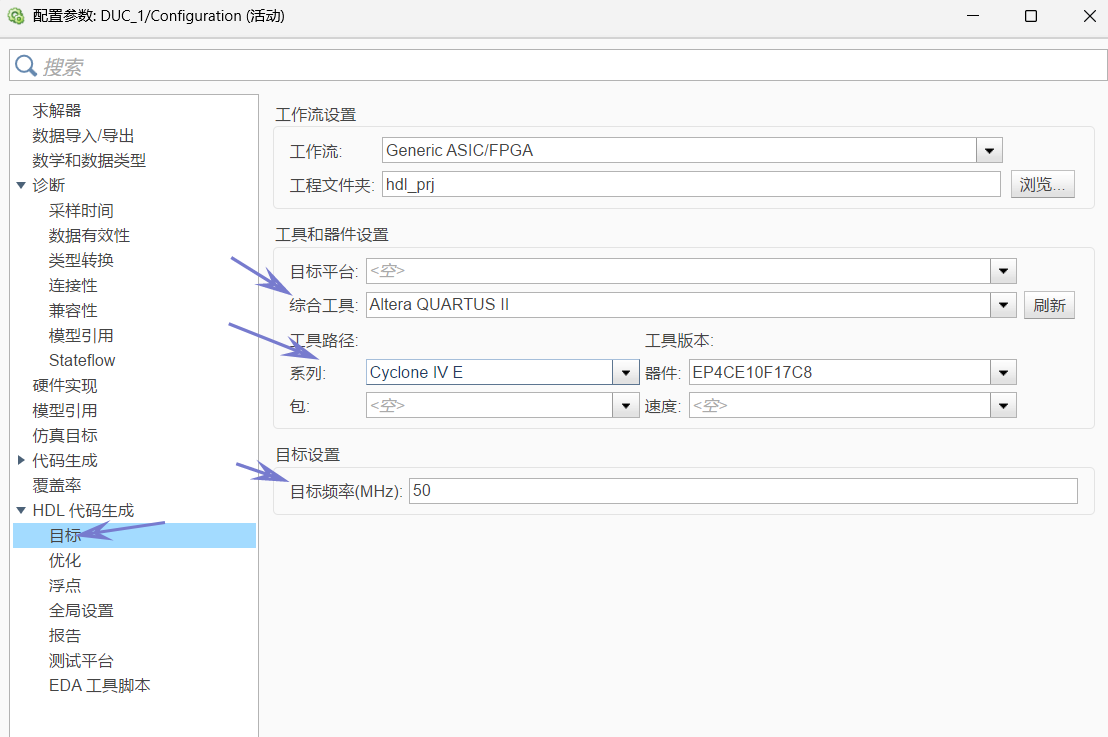

目标平台选择

根据使用的FPGA选择综合工具和FPGA的系列。

模块设置

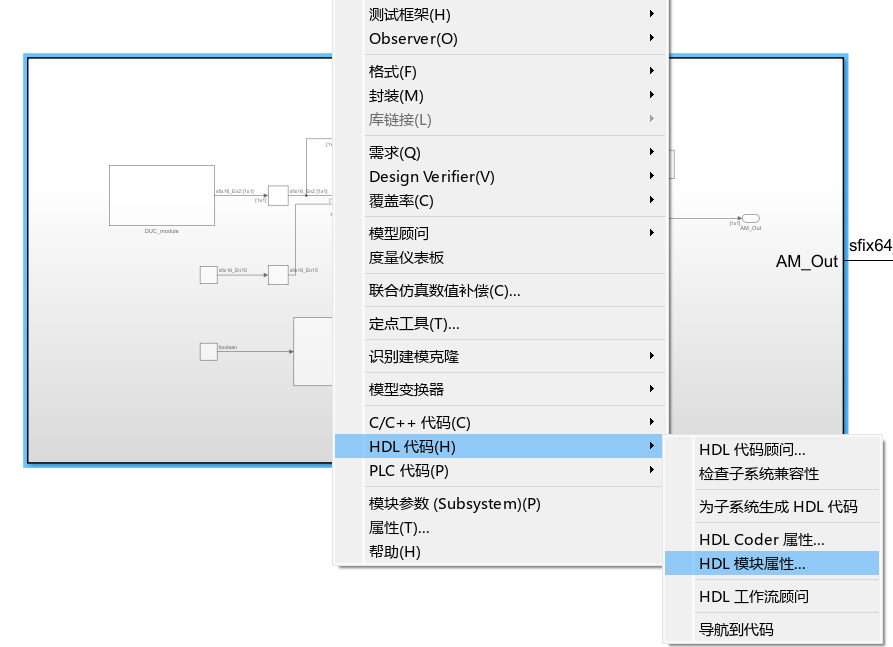

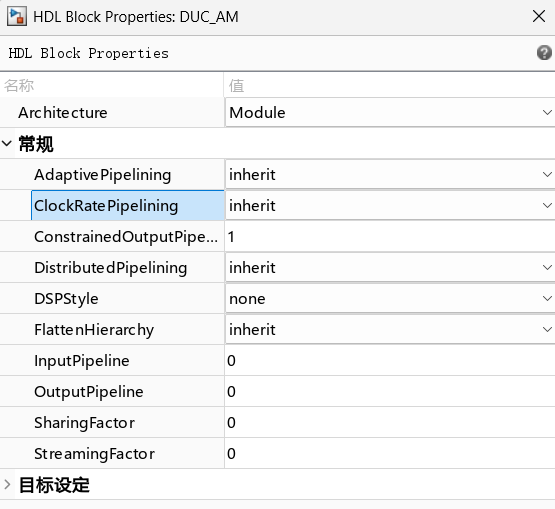

在要生成代码的子系统上右键,选择HDL模块属性:

可以对流水线、乘法器等参数进行设置

如果生成的代码在EDA工具中编译以后无法满足时序约束,可以加输入和输出的流水线

💡 如果模块的输出对前面的模块有反馈信号的话不能添加流水线,详细见

bookmark

[bookmark](https://blog.sawenmoerjie.top/article/ec96aebc-b5a5-4059-bbef-02f0003e7a45)

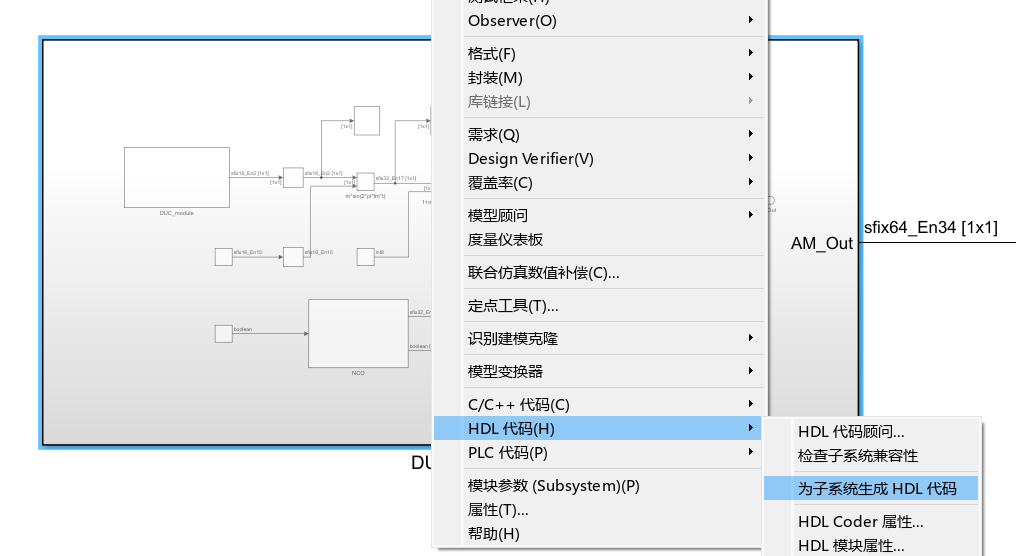

代码生成

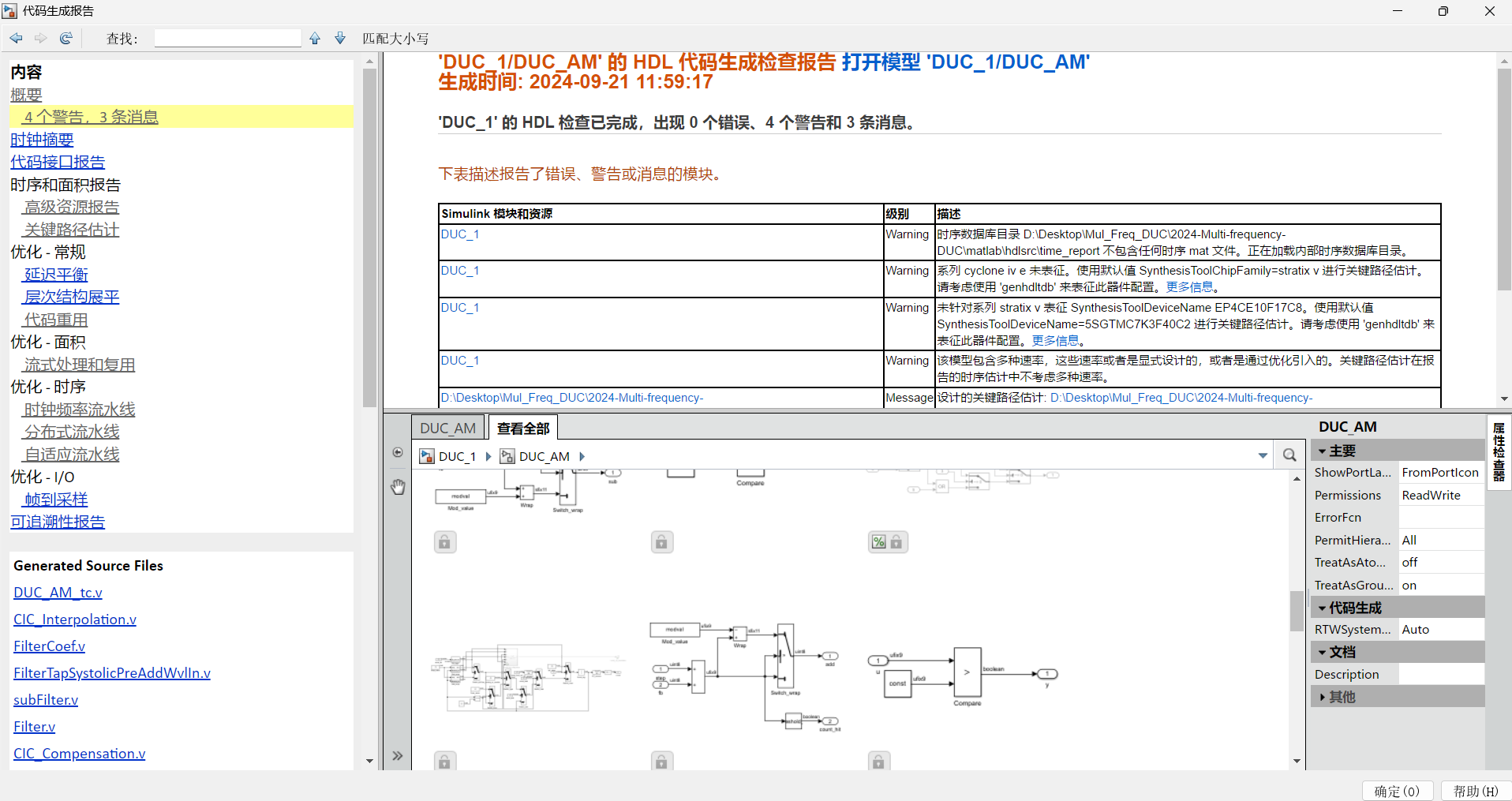

点击为子系统生成HDL代码后会自动进行一次编译,命令行窗口会出现如下信息

同时会生成一个report

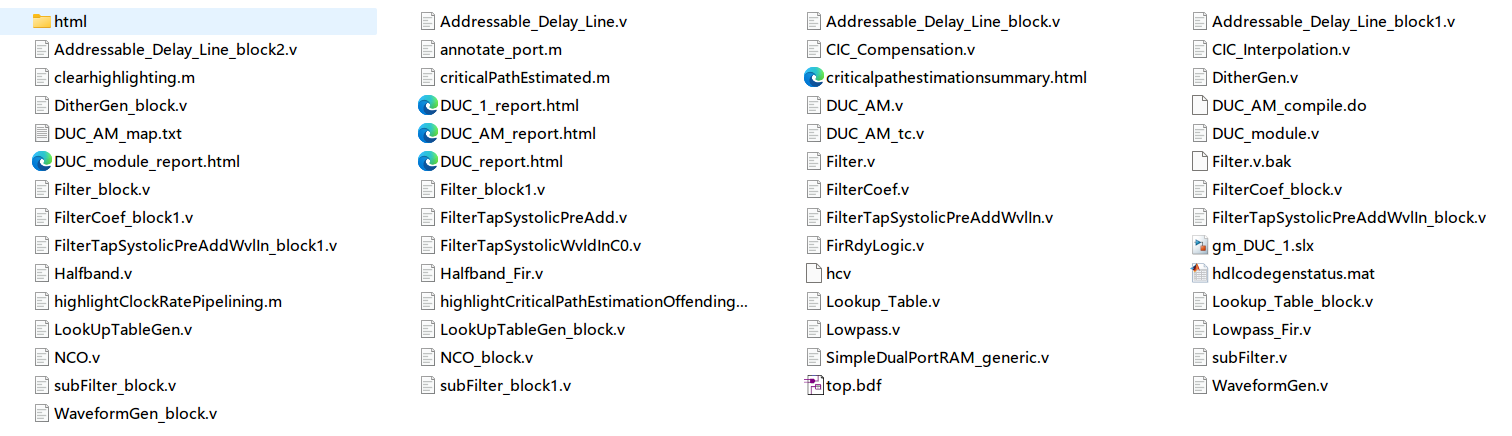

没有报错的话即可在上面选择的文件夹里面看到生成的Verilog代码文件

将这些文件导入到EDA工具中即可直接例化使用。

💡 所有文件都要导入,不能只导入需要的某个名字的模块!

原文地址:https://blog.csdn.net/qq_66439282/article/details/142463128

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!