【更新中】《硬件架构的艺术》笔记(二):时钟与复位

本章主要针对ASIC设计给出建议,独立于CAD工具以及工艺,主要针对模块设计和存储器接口。

同步设计

这是对时钟域控制最安全的方法,单个主时钟和单个主置位/复位信号驱动设计中所有时序器件。

避免使用行波计数器

行波计数器:用触发器的输出来驱动其他触发器的时钟输入,一般会存在问题。此时触发器的时钟并不是同步的,存在相位偏移,若该触发器链很长,延迟累积,会导致采样到错误的数据。

门控时钟

门控单元会导致时钟偏移,并会引入尖峰脉冲单元作用于触发器。可能仿真正常,综合出问题。

门控时钟作为低功耗设计的常用方法,通常由DC工具插入,在RTL除auto_clock_gating控制外,不要对时钟做任何处理

双边沿或混合边沿时钟

缺点:

- 复杂性增加:使用双边沿时钟会导致设计的复杂性增加。电路设计师必须确保在两个边沿上对信号的处理是同步的,并且要处理好时序问题。

- 同步复位问题:在使用同步复位的电路中,复位信号必须在时钟的某一边沿有效。双边沿时钟可能导致复位信号在不同边沿上产生不同的行为,从而增加了调试和验证的复杂性。

- 插入扫描链的困难:在测试过程中,插入扫描链时,双边沿时钟可能会导致信号路径的确认变得更加困难。因为在一个时钟周期内,信号在不同边沿上可能会有不同的状态,这使得测试和验证变得更加复杂。

- 信号路径的时序问题:由于信号在两个边沿上都可能被采样,设计者需要更加小心地确认信号路径的时序,确保在时钟的每个边沿上,所有相关信号都能在正确的时序下稳定。

不过有时候为了追求性能还是会使用双边沿,如DDR。

用触发器驱动另一个触发器的异步复位端

第二级输出同时受时钟边沿和复位信号影响,违反了同步设计原理,第二级触发器的时钟和复位之间存在潜在的竞争条件。

推荐的设计技术

要理解综合工具如何对不同的HDL编码风格和结果进行解释(硬件思维),其会影响设计门数和时序性

避免在设计中出现组合环路

在同步设计中,所有反馈回路都应包含寄存器,组合环路违背了同步设计原理。组合环路是不可综合的。

解决方法:引入一个触发器或者寄存器。

许多设计工具中,组合环路都会导致无休止的循环计算,所以EDA可能以不同的方式把组合环路打断,导致于原始设计意图不一致。

避免数字设计中的延迟链

延迟链:两个或多个单扇入单扇出的连续节点产生延迟。通常使用反相器链在一起。

使用场景:异步设计中,解决其他组合逻辑导致的竞争条件。

缺点:增加设计对操作环境的敏感性,降低设计的可靠度,增加移植到不同器件结构上的难度。

避免使用延时链,需要在设计中使用同步技术取代异步技术。

避免使用异步脉冲产生器

两种脉冲产生的方法(纯异步):

- 同一个信号接两输入与门或者或门,其中一个取反或者加延迟链,脉宽取决于两个信号相对延迟。(相当于人为增加毛刺宽度)

- 寄存器输出延迟后驱动同一个寄存器的异步复位端。

异步产生的脉冲宽度常常为综合和布局布线软件带来困难,实际脉宽只有在布局布线之后,布线和传播延迟已知时才能确定。所以在创建HDL时很难得到可靠的延迟值,且PVT(压力、体积、温度)环境,工艺脉宽都会变。除此之外,STA不能验证脉宽,验证工作会变得困难。

由于涉及对脉冲数量的控制,所以多脉冲结构会比脉冲产生器引起更多问题。多脉冲也增加了设计的频率。

推荐使用的同步脉冲产生器:

这个结构脉宽总是于时钟周期宽度相等,可以用时序分析验证,易于移植,独立于工艺。

always@(posedge clk)

begin

q2<=q1;

q1<=d;

end

assign Pulse=q1&~q2;

这里有点问题,经过触发器后触发信号延后了一个周期,脉冲应该也延后一个周期。

类似的,可以在触发输入末端产生脉冲的脉冲产生器。

避免使用锁存器

图中电路X和Y同时拉高,形成了一个类似组合环路的结构,会使电路振荡。

原因:Latch的触发信号高电平时,输出对于输入来说是“透明的”。

- STA分析器通常会做出与锁存器透明有关的错误假设:要么发现伪路径,要么丢失真正的关键路径。

- 寄存器本身时序也是模糊的。这样的代码很难移植或者复用。

- 锁存器常常使电路不可测。

- FPGA是寄存器密集型电路,所以使用latch会占用更多资源。

- 不完整的if或者case会导致意料外的的latch的生成(因为组合电路要保持之前的值就得用latch)。

- 对于某些不支持Latch的FPGA,就会综合出组合环路代替Latch。

图中电路有锁存数据的能力,但是可能违背建立时间和保持时间的要求,而且很难发现。

Latch也并不是完全没用,事实上可以用Latch挪用周且或者借用时间来满足关键路径的要求。

避免使用双沿时钟

双沿时钟使得数据传输在给定的时钟速率下能达到双倍的吞吐率,但违背了同步电路原理,会引发以下问题:

等效同步电路:

上述等价是在时钟占空比为50%时成立的,如果时钟非对称占空比可能导致违背建立和保持时间,扫描路径也不能容易地通过触发器。

使用条件:对性能/速度要求很高、且无法承受使用等效同步电路在DFT和验证方面带来的额外开支。

优点

1、提升性能。

2、降低功耗。

时钟方案

内部产生的时钟

应尽量避免內部产生时钟。组合逻辑产生时钟会引入毛刺,也会引起时序方面的问题。同步时序电路数据的毛刺不会引起任何问题,而毛刺出现在时钟输入端或异步输入端就会产生明显的影响。

毛刺到达时钟输入端如果数据变化,会违背建立和保持时间。即使没有违背时序要求,寄存器也可能输出意料外的值。毛刺可能导致计数器增加额外的计数值,如图。

解决方法:组合逻辑输出增加一个寄存器输出,这个寄存器可以阻止组合逻辑产生的毛刺。

组合逻辑时钟也会增加时钟延迟,可能导致违背时序要求。

图中由于时钟偏移导致违背了建立时间。

一种减少时钟偏移的方法:将产生的时钟放到SoC中高扇出且低偏移值的时钟树上。

分频时钟

设计中要保证大多数时钟来自于PLL,避免异步时钟分频逻辑引起的许多问题。对主时钟分频时应使用同步计数器或状态机。

保证总是由寄存器直接产生分频时钟信号,不要使用组合逻辑避免毛刺和尖峰脉冲。

行波技术器

使用行波计数器对时钟进行幂为2的分频。

优点:使用的门更少。

缺点:对STA和综合工具带来麻烦,应尽量避免。

功耗较高的系统中很适合使用这种计数器,可以大量降低由逻辑或SoC所引起的峰值功耗。

需要处理多个频率标准的通信应用常常使用多个时钟。

使用多路时钟的前提:

同步时钟使能和门控时钟

优点:减少功耗。

缺点:不是同步设计,显著增加设计时间和验证的工作量。增加时钟偏移并对毛刺敏感,所以能导致设计失败。

可以使用同步的时钟使能,用纯同步的方法关闭时钟域,但这样时钟树一直保持反转,触发器保持内部活跃,无法降低功耗。

这里通过选通信号选择触发器输入,但是并没有真正意义上关闭触发器,只是使其值保持。

门控时钟方法学

同步设计中,功耗主要有三个部分:

对时钟门控能够大幅降低触发器的功耗,门控可以在时钟数的根部、末端或者两者之间的任何位置。

时钟数几乎消耗了整个芯片功耗的50%,所以最好在根部产生或者关闭时钟。

不带锁存器的门控时钟电路

使用与门、或门实现。为避免过早截断或产生多个时钟脉冲、应强制要求使能在时钟上升沿到下降沿一直保持常量。该限制使得基于单时钟触发器的设计中不适合使用不含锁存器的门控时钟。(因为对使能信号有较高的要求)

图中为过早截断的情况。

基于锁存器的门控时钟电路

使用锁存器就可以使门控时钟电路不需要满足上面的条件了。

使用与门控制上升沿有效的时钟,反之使用或门控制。

这个电路在使能关闭时为低电平,当打开时便不会漏掉下降沿。

使用这项技术时,使能信号必须在半时钟周期内产生。(锁存器只在半个时钟周期内具有锁存功能)

要保证设计中所有时钟能同时使能以便DFT,可以再加一个或门。

门控信号

特殊部分使用门控信号提高能效。(感觉这里的意思就是减少组合逻辑的功耗)

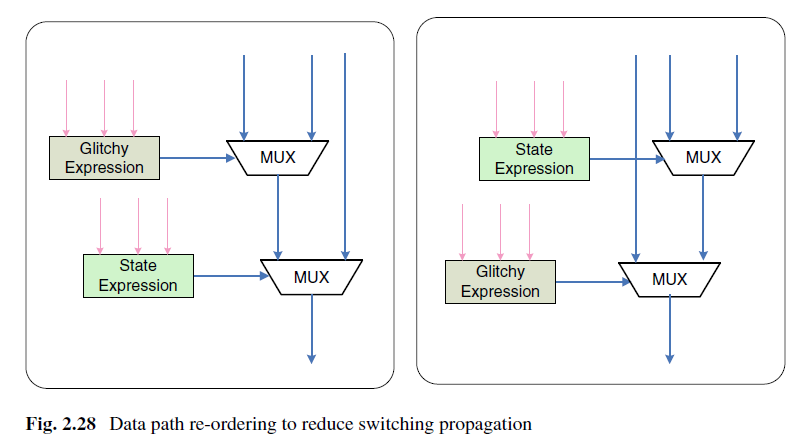

重组数据路径以减少转换传播

把容易产生毛刺或者会经常翻转电平的电路放在电路后级,可以减少转换传播从而降低功耗。

原文地址:https://blog.csdn.net/qq_38156104/article/details/143706005

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!