Marin说PCB之LPDDR5的布线注意事项--03

之前我们已经把大的DDRC0-channel的所有BUS线的分组做好了,接着就是按照前面手册给出的等长设计要求去建等长的group了。每个组的等长设计要求如下所示:

1,Command and Address Signal Group

1,地址线的等长group:DRRC-CA-A,我们在设置等长的时候尽量比手册的给的误差值稍微严一些,手册给的可能比较宽松一些,因为我们在实际上走线的时候不是那么完美的,都会多少有一些信号完整性的问题,例如串扰,反射等。

2,地址线的等长group设置如下所示:DRRC-CA-B

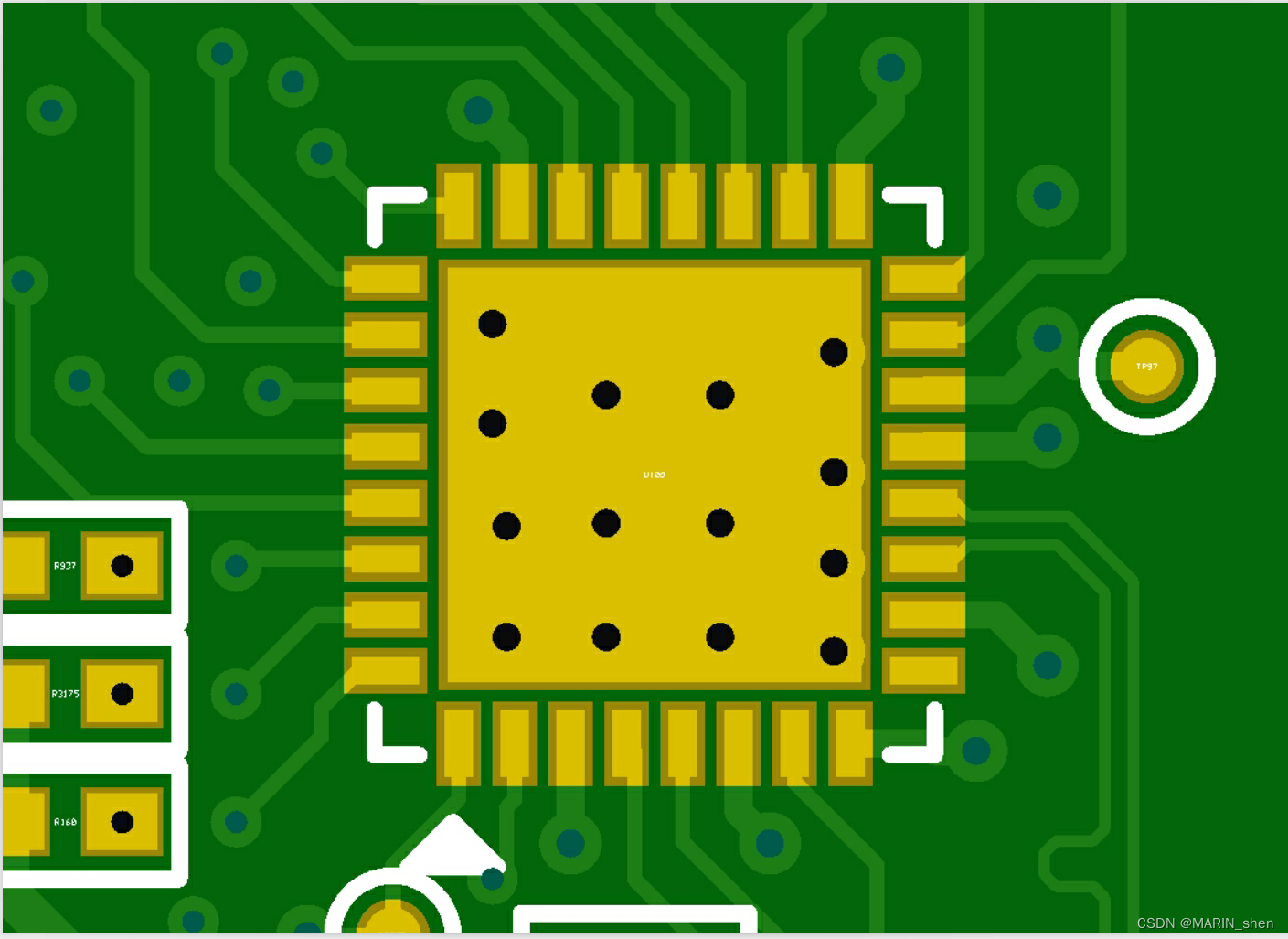

3, 大的DDRC0-channel中四组数据group设置如下所示:

这个规则中是把每个字节中的WCK to RDQS 以及DM / DQ to WCK等长规则都加到了DM / DQ这个等长规则中去了,因为芯片手册上的设计要求中的DM / DQ这个group的等长误差是+-50MIL, WCK to RDQS的等长group的规则是62.5MIL,DM / DQ to WCK等长group的规则是相对松一些是150MIL,

这个里面还有一个换PIN 的原则就是一组DATA0里面的9个信号是不能互相换PIN的,但是一个小的channelA里面Byte0-1可以整体和channelB里面Byte2-3互换。

1,No DQ bit swap allowed .( 不允许DQ之间位交换)。

2,Byte swap is allowed only within the same channel.(仅允许在同一通道内进行字节交换)

一个64位的DDR颗粒上需要建的group有12个,总的有四片DDR颗粒需要的建的等长group就有48个了,也算是一个浩大的工程了。

其实上面的等长规则还是建少了一些的,例如手册上要求的每个channel的WCK0:1,WCK2:3等长误差在+-488MIL,这个规则建议还是补上去吧。

• WCK_[1:0] (per channel-A) matching within + / - 488 mils (or + / - 78 ps skew)

• WCK_[3:2] (per channel-B) matching within + / - 488 mils (or + / - 78 ps skew)

只是这个板子刚刚好channel-A的WCK0布线长度和WCK1的布线长度误差不到100MIL。

关于单板上的DDR的所有差分信号的N和P等长误差就不再这里赘述了。

这个要求只是一个示例,不同的项目要求会有所不同的,要懂得变通。以上就是本期的所有内容了,我们下期文章不见不散。

下面是小编的微信公众号二维码,习惯用微信看的可以扫描下面的二维码关注小编即可阅读文章。

原文地址:https://blog.csdn.net/weixin_45223454/article/details/140556532

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!