理解ADC:ADC的分辨率、采样率、带宽之间有什么关联?(讲的不是采样定理)

前言

ADC 的分辨率、采样率、带宽,这几个参数之间似乎存在某种关联,今天我们来“定性”(也就是简单)分析一下。

采样-保持电路

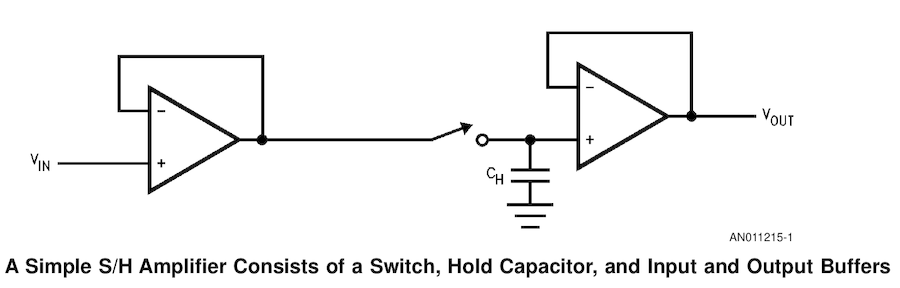

首先从 ADC 的“采样-保持电路”( Sample & Hold )说起,一种简化图示如下:

图1 ADC 采样保持电路,来源[1]

这部分的核心是电容。

当开关闭合时, 电路处于采样模式,外部信号给电容充电;当开关断开时, 电路处于保持模式,期间 ADC 进行模数转换。

电容的瞬态响应

采样、保持两种模式的转变,并不一蹴而就,而是有一个演变过程,称为瞬态响应( Transient Response ),用时域波形图示如下:

图2 电容上的瞬态响应,来源[2]

图中蓝色虚线是外部信号,红色实线是电容上的信号。

其中有几处关于“时间”的定义:

- Acquisition time:电容获取(跟随)外部信号电压所需时间;

- Aperture time:由于时钟抖动和噪声导致的不确定性,称为孔径时间;

- Settling time:电容稳定的保持住某个电压所需时间;

特别的,在 Settling time 内,信号看起来发生了小部分振荡, 这对于存在容抗的交流电路是潜在现象,猜猜它会影响什么?

Settling time 与分辨率

ADC 的分辨率用 bit 位数表示,分辨率越高,LSB( Least Significant Bit )幅度越小。

振荡信号经由时间衰减,并趋向稳定,我们的目的是让振荡信号的振幅最终稳定在 1/2 LSB 幅度内,不能跳跃。如果分辨率越高,也就是 LSB 越小,也就要等待更久的时间,才能让振荡信号变得足够“稳定”。

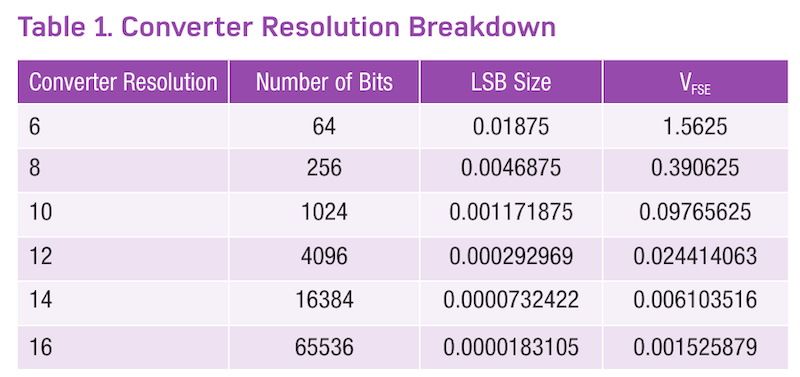

在 ADI 的文章 “Put an End to High Speed Converter Bandwidth Terms” [3] 中描述了这种关系,它将 ADC 不同分辨率(Converter Resolution),量化阶梯数量(Number of Bits)、LSB 幅度(LSB Size)、满量程误差(Full-scale error,FSE)等罗列如下:

图3 ADC 分辨率、LSB、与Error,来源[3]

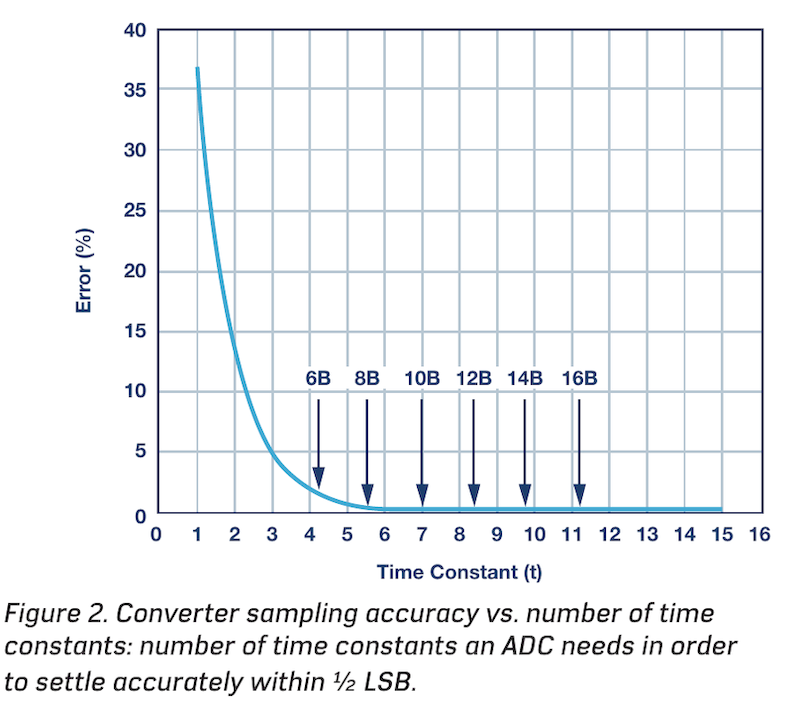

然后,振荡信号的周期是一个常数,它与电路本身的 R、C 等参数有关。不同分辨率情况下的 Settling time 可以用这个常数的“倍数”来衡量:

图4 ADC 不同分辨率所需 Setting Time 是时间常数的倍数,来源[4]

比如,在同样电路下,一个 12 位 ADC 的 Settling time,需要等待 8.4 倍的时间常数(图中 12B 的箭头),才能使振荡信号稳定在 1/2 LSB 以内。

采样率,受到什么影响?

了解上述之后,再看采样率就比较简单。

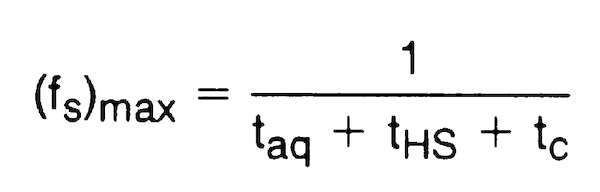

ADC 的一个采样周期,所需的最少时间是 Acquisition time + Aperture time + Settling time + Conversion time。在参考资料[1] 中用公式表示如下,其中忽略了Aperture time,HS 意为 Hold Mode Settling Time :

图5 ADC 最大采样率的计算公式,来源[1]

如果只考虑公式里的这些变量,可以得出,ADC 获取更高的分辨率(bit 位数),需要更久的 Settling time,那么,采样率也只能更低。

带宽,受到什么影响?

上述内容似乎没有带宽什么事,但别忘了在采样-保持电路里面有电容,隐含也有电阻(如开关的内阻),这就形成一种 RC 滤波器。

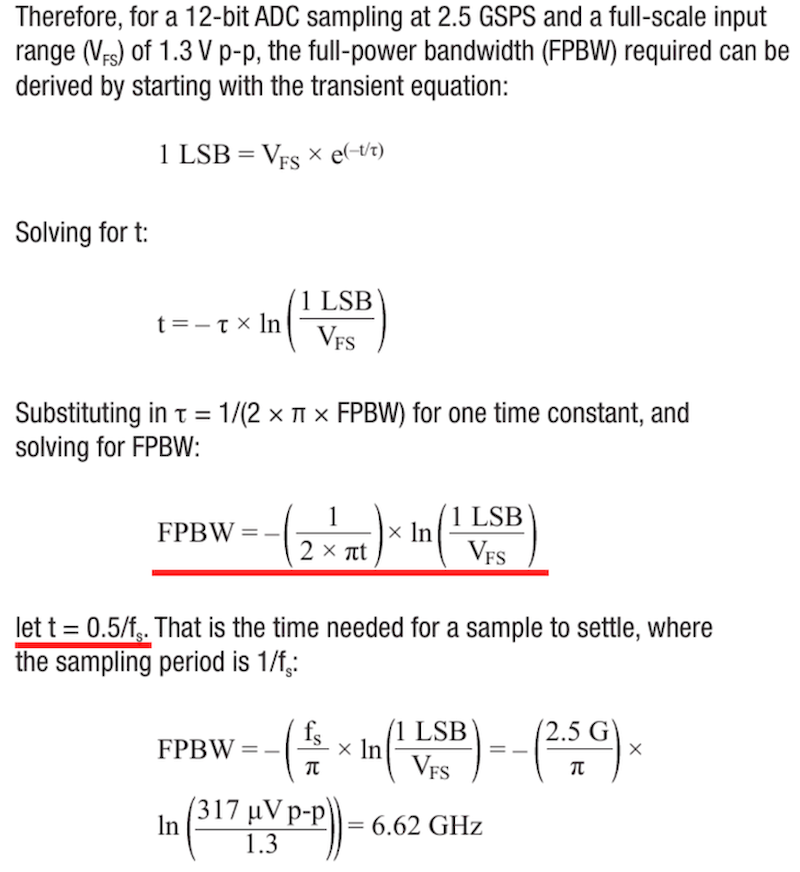

在 ADI 的文章 [3] 中举了一个例子, 说 ADC 的采样率是 2.5 GSPS,12-bit,1.3 V Full scale,求 ADC 所需带宽,计算过程如下:

图6 ADC 带宽与采样率,来源[3]

其中 ADC 的带宽(Full Power Bandwidth,FPBW)与采样率的关系,用红线标出。最终计算结果是,2.5 GSPS 需要 6.62 GHz 带宽。

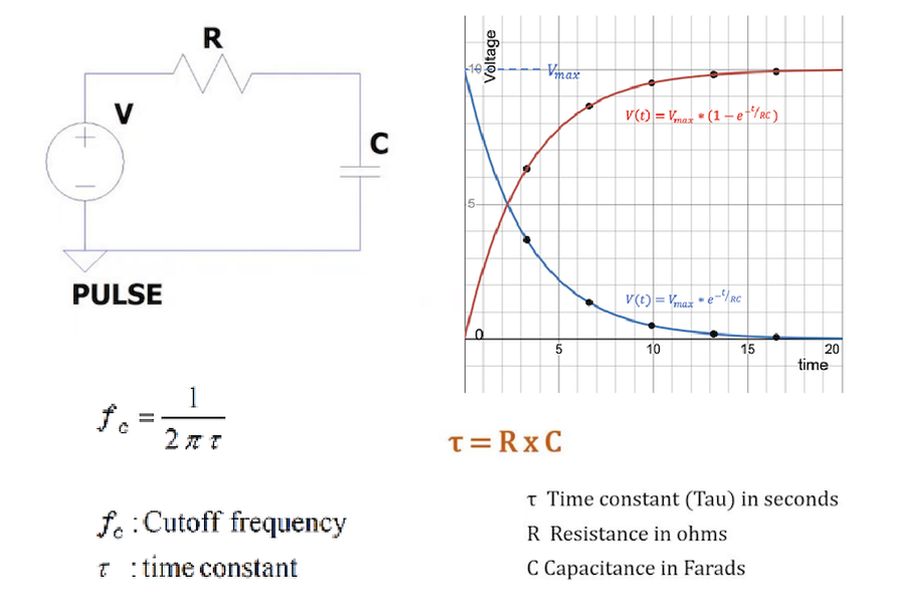

不过这是一种简化的模型,文中提到了一阶极点( Single-pole ),感觉就是将采样-保持电路简化为 RC 滤波器来算的,RC 滤波器的特性如下:

图7 RC 电路特性

总之,这个例子告诉我们,ADC 带宽 受到了采样-保持电路中 RC 的影响。

实际的采样-保持电路更为复杂,比如图1 中就展示了前后还有运放构成的电压跟随器,可能还有不同的反馈、差分、时钟等连接,因此实际 ADC 带宽 受到的影响因素更为复杂。

“ADC 带宽” 的定义

我看了 ADI、TI 文章(参考资料[4] [5] )中关于 “ADC 带宽” 的定义,对应英文 Full Power Bandwidth,相关 datasheet 中也有列出,指 ADC 能够准确传递信号且不产生明显衰减的频率范围,也就是发生 3dB 衰减时的频率,看着与运放带宽的定义类似:

Full Power Bandwidth (MHz): Analog input bandwidth is the analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB.

我理解在 ADC 选型时,优先看 “ADC 带宽” 的情况可能是对于 RF Intermediate Frequency 接收机或者需要降采样(Undersampling)的场景。

而对于传感器的 ADC 选型,优先看的可能还是采样率(或 分辨率、SNR)等指标。比如我们知道某个传感器的信号,其 DC 至最大频率范围,即“信号带宽”,选择采样率大于 2 倍信号带宽的 ADC,以符合奈奎斯特采样定理。

参考资料

参考资料均可以通过搜索关键词获取,查阅原文:

- TI SNOA223: Application Note 775 Specifications and Architectures of Sample-and-Hold Amplifiers

- https://www.digikey.be/en/articles/analog-fundamentals-sample-and-hold-circuits-work-adc-accuracy

- ADI StudentZone—November 2017 Put an End to High Speed Converter Bandwidth Terms

- ADI AN-835: Understanding High Speed ADC Testing and Evaluation

- TI Useful Things to Know about High-Speed A/D Converters

欢迎关注我的微信公众号“疯狂的运放”,及时收到最新的推文。

原文地址:https://blog.csdn.net/gilbertjuly/article/details/143577244

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!