[GICv3] 1.引言Introduction

基本概念

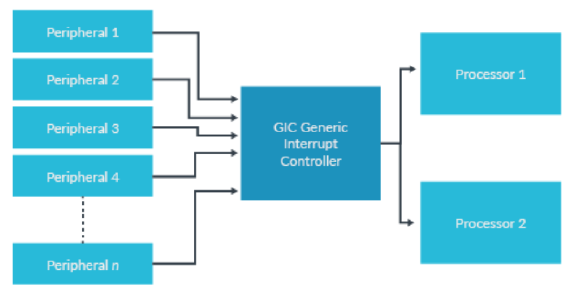

通用中断控制器 (GIC) 从外设获取中断,确定它们的优先级,然后将它们传送到适当的处理器内核。 下图了为一个 GIC 从 n 个不同的外设获取中断,并将它们分配给两个不同的处理器。

GCI(Generic Interrupt Controller),GICv3与Armv8-A、Armv9-A和Armv8-R兼容。

支持:

- Armv8和Armv9架构。

- 中断掩蔽和优先排序。

- 单处理器和多处理器系统。

- 电管理环境中的唤醒事件。

GIC负责产生中断,而ARM负责处理中断。因为GICv4是GICv3的扩展,除非另有明确说明,GICv3的所有定义都同样适用于GICv4。

系统结构

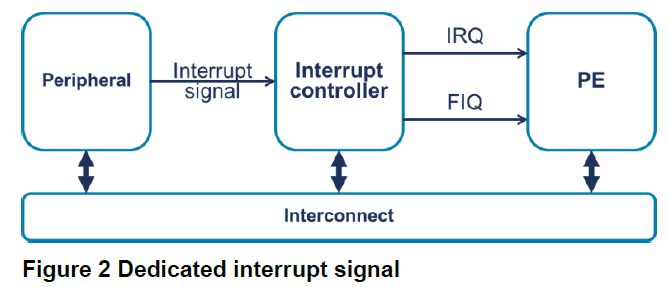

普通基于信号线的中断

该场景下,外设使用专用中断信号线通知GIC产生了中断,GIC进行中断优先级仲裁后产生IRQ信号或者FIQ信号给到PE。

在ARMv8体系结构中,IRQ和FIQ为两种不同的中断类型,无优先级高低之分,服务于不同的应用场景。GIC向PE递交IRQ还是FIQ取决于中断分组、当前PE所处的安全状态和异常等级。

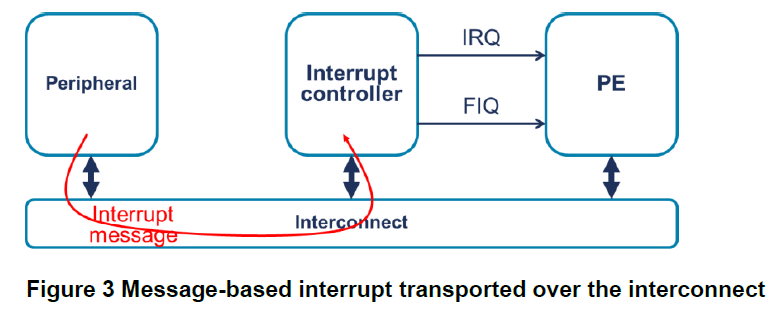

message-based中断

使用消息(message)将中断从外设转发到中断控制器,无需每个中断源都有专用信号。 这对于大型系统的硬件设计人员来说是一个优势,其中可能有数百甚至数千个信号通过 SoC 路由并汇聚到中断控制器上。

支持的中断类型

- 本地外设中断(LPI)。

- 私有外设中断(PPI)。

- 软件生成中断(SGI)。

- 共享外设中断(SPIs)。

支持边缘触发和电平触发:

-

边沿触发

在检测到中断信号的上升沿时断言的,然后,无论信号的状态如何,都会一直断言,直到中断被软件确认(ack)。

-

电平触发

中断信号电平处于活动状态,它就会被断言,只要电平不处于活动状态,它就会被取消断言(assert)。它由软件取消断言。

中断状态

-

Inactive

中断没发生或者已经被cpu处理完成了

-

Pending

中断已经被硬件触发或软件产生(SGI),但cpu还没有应答中断

-

Active

cpu已经应答并正在处理中断。

-

Active and pending

中断正在处理,然后又有中断pending了

中断处理模型(Models for handling interrupts)

-

Targeted distribution model

这个模型适用于所有PPI和所有LPI。由软件指定的目标PE会收到中断。

-

Targeted list model

这个模型只适用于SGI。多个PE独立接收中断。当一个PE确认中断时,中断的待定状态只对该PE被清除。中断对每个PE来说都是独立待定的,直到它被PE确认。

-

1 of N model

这个模型只适用于SPI。中断是针对一组指定的PE,并且只针对该组中的一个PE。Arm GIC架构保证了中断只呈现给目标PE集中的一个PE。

原文地址:https://blog.csdn.net/qq_27350133/article/details/140332808

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!