Verilog仿真跨模块调用内部信号的方法

在Verilog仿真时如果需要调用某子模块中的信号在本模块中使用可以使用层次化引用的方法,而不需要在rtl部分用端口引出来。

引用方式:当前例化模块名.子例化模块名.子子例化模块名.参数 将需要的信号引出。

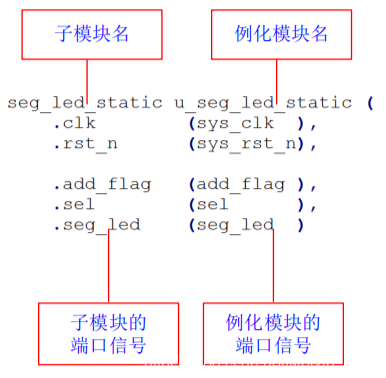

注意是用例化模块名而不是用子模块名,两者区别如下:

如示例代码中的有两处分别引用不同子模块中的信号在本模块使用。

`timescale 1ns/1ns

module tb_top();

wire i_rst_n ;

assign i_rst_n= u_top.u_ctrl.w_sys_rst_n;

reg [7:0] data_in;

reg clr_n;

initial begin

i_clk = 1'b1;

clr_n <= 1'b0;

data_in <=8'b0;

#520

wait (u_top.u_trig.w_sam_en == 1'b1)begin

clr_n <= 1'b1;

data_in <=8'h5A;

end

top u_top(

.i_ext_clk (i_clk),

.o_spi_sclk (o_spi_sclk ),

.o_spi_mosi (o_spi_mosi),

.i_spi_miso (i_spi_miso )

);

//==========================< Clock block >============================

always #10i_clk = ~i_clk;

endmodule

实际上有多种层级引用方式:可参考Verilog基础:标识符的向上向下层次名引用

原文地址:https://blog.csdn.net/weixin_48412658/article/details/137872009

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!