PCIE V3.0物理层协议学习笔记

一、说明

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。

PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能。

V3.0版本最大的变更是支持8Gbps的速率,以及为实现带宽翻倍使用了128b/132b的高效编码技术。同时,仍是支持2.5Gbps和5Gbps的传输速率(8b/10b编码)。

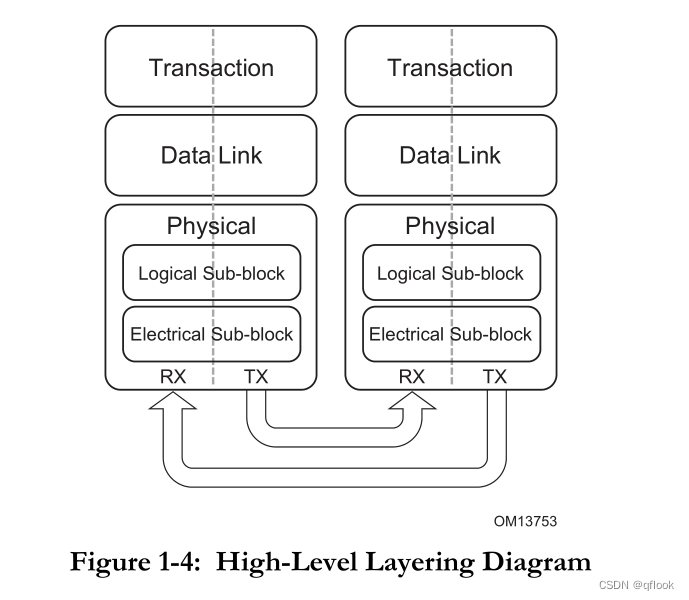

分层框图如下,本文主要讲的物理层Physical主要包括逻辑部分和电气部分,主要包括PLL电路、Buffer、阻抗匹配电路、驱动电路、串并转换或并串转换电路及均衡电路等;逻辑子模块的功能是负责数据链路层和电气子模块的交互,例如有多lane的情况下,将从数据链路层的数据拆分,并8b/10b编码给到电气子模块等:

数据结构如下:

数据结构如下:

传输性能分析:https://zhuanlan.zhihu.com/p/645335755?utm_id=0

二、电气要求

1.发送规范

1)测量环境

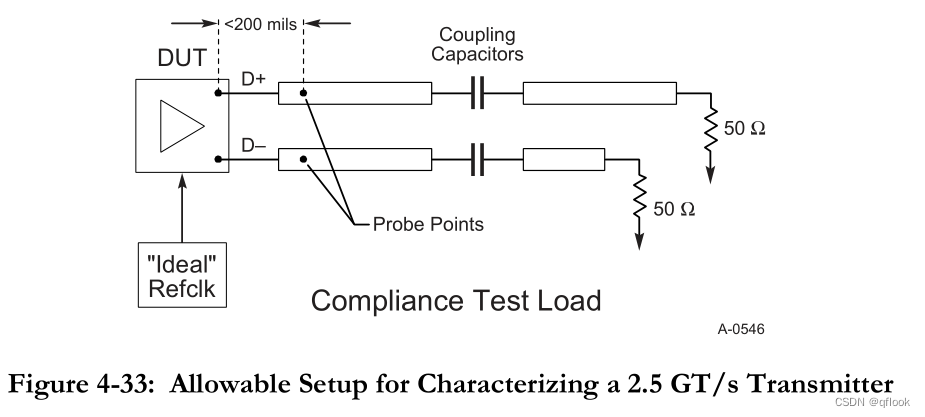

2.5Gbps速率可以直接用探头测试,需注意探针要距离TX管脚不超过200mils,且在AC耦合电容之前。环境如下:

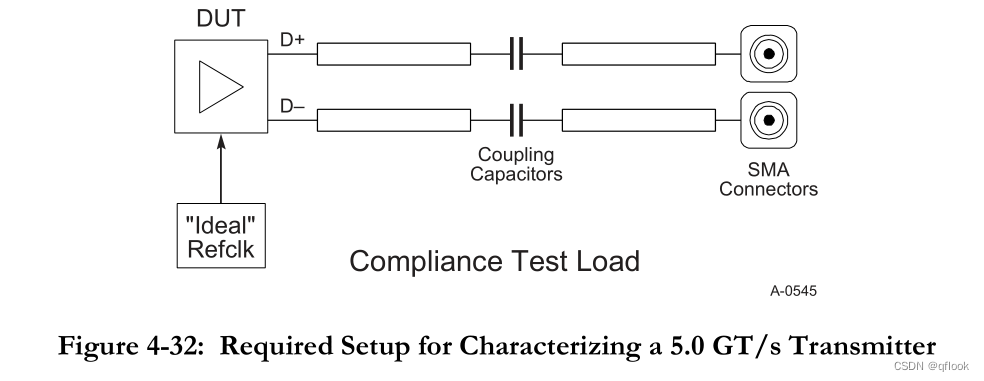

5Gbps速率不能直接用探头点测(前端电容、引线长度导致的寄生参数等),需要用SMA直接接到示波器,环境如下:

另外,需要说明的是,以上两种速率也可以用通用的测试夹具进行测试,不过需要通过去嵌等手段去除夹具的影响。

另外,需要说明的是,以上两种速率也可以用通用的测试夹具进行测试,不过需要通过去嵌等手段去除夹具的影响。

对于8Gbps速率来说,则需要特制的测试板来实现测试目的,环境如下:

其中低抖动时钟源是为了测量抖动时排除外部干扰;Breakout Channel疏导通道是由于芯片管脚(特别是BGA封装)无法直接测试,也因此需要本通道尽量短(不超过6英寸),插损不能超过2dB,回损不能高于15dB(4G频率范围内);Replica Channel复制通道应尽量和疏导通道一样(走线长度、过孔、所在层数等),方便去嵌操作。

2)TX均衡

2.5Gbps和5Gbps两种速率仅支持去加重均衡技术,其中2.5Gbps只支持-3.5dB去加重,5Gbps支持-3.5dB和-6dB两种去加重规格。

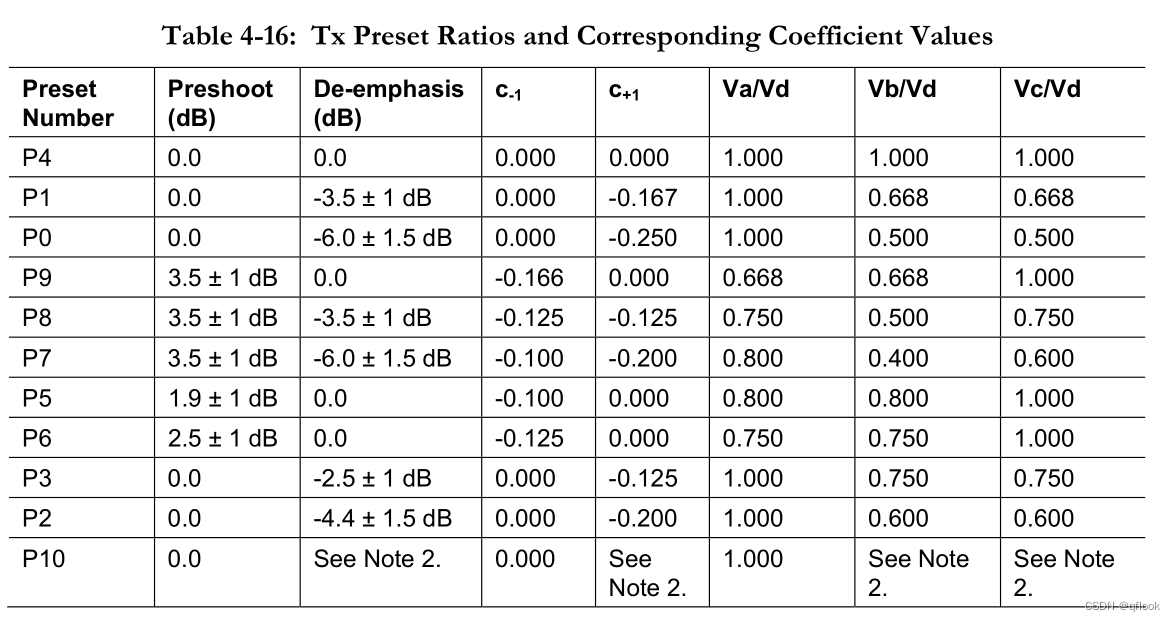

8Gbps的TX均衡比较复杂,通过3抽头滤波器实现11中均衡组合(具体均衡实现方法参考:

mp.weixin.qq.com),具体如下:

其中全摆幅需要支持全部均衡,Reduced swing低摆幅仅需支持P1、P3、P4、P5、P6和P9即可。以上组合中的P0和P1也就是2.5G和5G的去加重,因此实现了兼容。

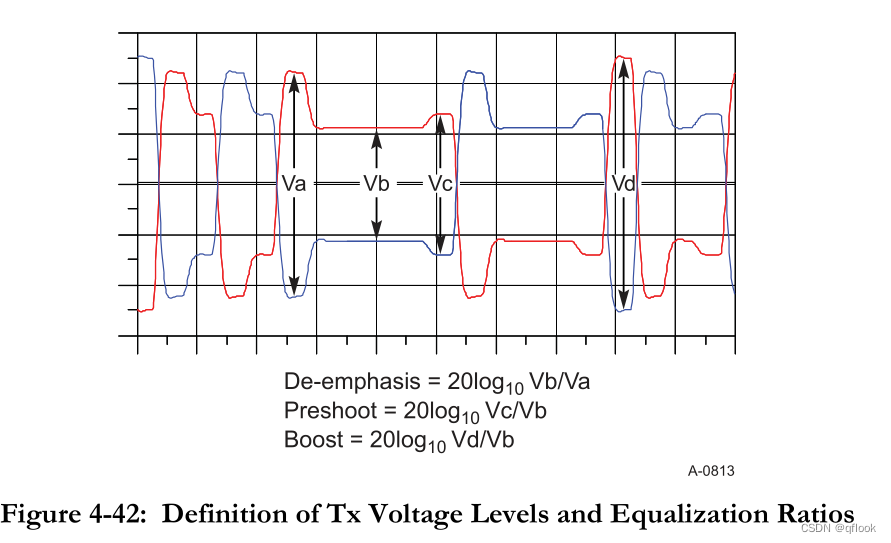

上表中的C就是指的抽头系数,通过不同系数来实现的不同均衡组合,也导致了信号波形的区别:

Vb就是指去加重电压,VC是指预充电压,Vd是指最大幅度电压,Va协议上也没有具体说明,个人认为是normal电压。

Vb就是指去加重电压,VC是指预充电压,Vd是指最大幅度电压,Va协议上也没有具体说明,个人认为是normal电压。

3)TX电器规范

协议明确规定了3种速率的TX参数,具体如下:

| Symbol | 2.5G | 5G | 8G | 备注 |

| UI | 399.88~400.12ps | 199.94~200.06ps | 124.9625~125.0375ps | 不包含扩频时钟SCC引入的抖动 |

| VTX-DIFF-PP | 0.8~1.2V | 0.8~1.2V | 无 | 全摆幅电压 |

| V TX-DIFF-PP-LOW | 0.4~1.2V | 0.4~1.2V | 无 | reduce摆幅电压 |

| V TX-DE-RATIO-3.5dB | 3~4dB | 3~4dB | 参考Table 4-16 | |

| V TX-DE-RATIO-6dB | 不支持 | 5.5~6.5dB | 参考Table 4-16 | |

| V TX-CM-AC-PP | 未规定 | ≤150mV | ≤150mV | AC共模电压峰峰值 |

| V TX-DC-CM | 0~3.6V | 0~3.6V | 0~3.6V | DC共模电压峰峰值 |

| Z TX-DIFF-DC | 80~120Ω | ≤120Ω | ≤120Ω | |

| L TX-SKEW | 【500ps,2UI】 | 【500ps,4UI】 | 【500ps,6UI】 | 差分对间偏差 |

| C TX | 【75,265nF】 | 【75,265nF】 | 【176,265nF】 | AC耦合电容 |

| Symbol | 8G | 备注 |

| V TX-FS-NO-EQ | 0.8~1.3V | 无TX均衡的全摆幅峰峰值电压 |

| V TX-RS-NO-EQ | ≤1.3V | 无TX均衡的低摆幅峰峰值电压 |

| V TX-EIEOS-FS | ≥250mV | EIEOS期间全摆幅电压最小值 |

| V TX-EIEOS-RS | ≥232mV | EIEOS期间低摆幅电压最小值 |

2.RX规范

1)2.5G的电气规范

具体要求如下:

| 参数 | 要求 | 备注 |

| UI | 399.88~400.12ps | 不包含SSC |

| 差分电压峰峰值 | 0.175~1.2V | |

| 眼宽 | ≥0.4UI | |

| 单端匹配电阻 | 40~60Ω | |

| 差分匹配电阻 | 80~120Ω | |

| 差分对间偏差 | ≤20ns | 5G是8ns,8G是6ns |

2)5G的电气规范

5G的RX要求分2种情况,一是TX和RX共用100MHz参考时钟,另外一个是数据嵌入式时钟。

眼图模板如下:

共用参考时钟的参数如下:

共用参考时钟的参数如下:

数据嵌入式时钟的参数如下:

3)8G的RX测试

RX主要进行容限测试,测试环境如下:

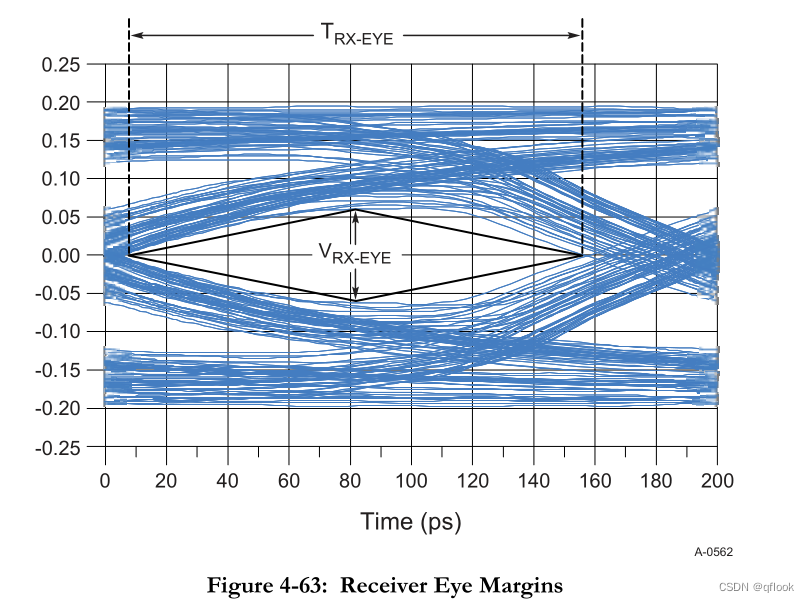

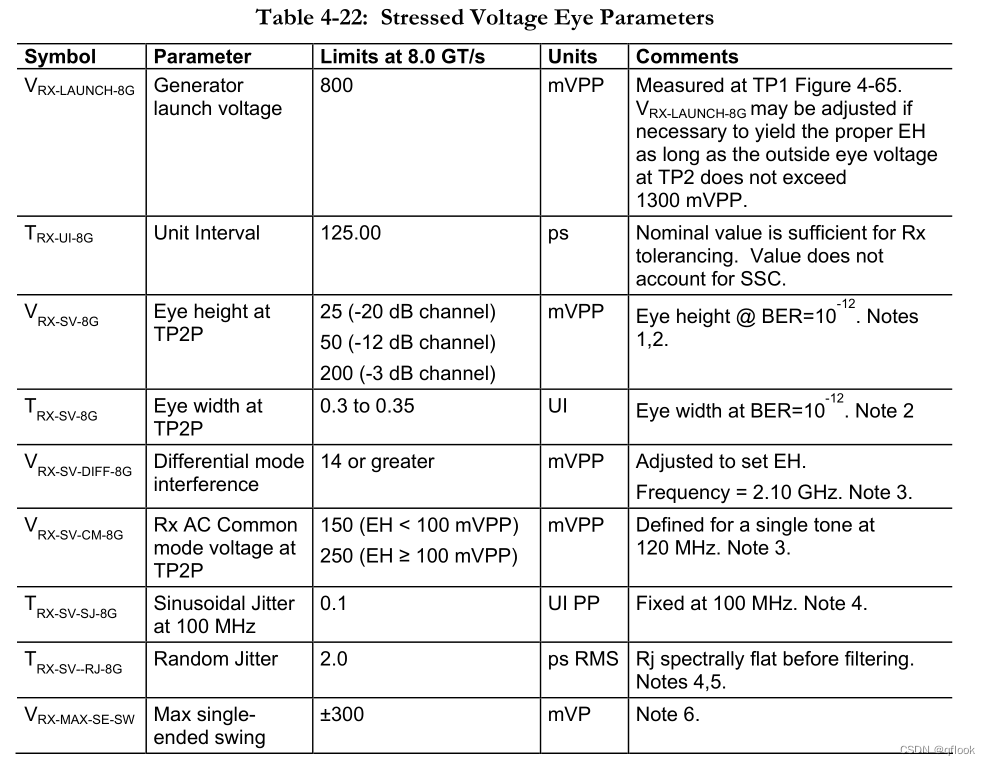

主要原理是校准通道和疏导通道模拟实际走线,信号发生器模拟TX,首先调整在TP2P位置测得的压力眼图(有2种眼图,分别测试电压和抖动,具体如Table 4-22和4-23),然后切换到#2通道将信号发送给RX,然后测试BER误码率要求小于10的-12次方。

主要原理是校准通道和疏导通道模拟实际走线,信号发生器模拟TX,首先调整在TP2P位置测得的压力眼图(有2种眼图,分别测试电压和抖动,具体如Table 4-22和4-23),然后切换到#2通道将信号发送给RX,然后测试BER误码率要求小于10的-12次方。

校准通道提供了3种,代表了真实情况遇到的最小到最大插损信道的情况:

校准通道提供了3种,代表了真实情况遇到的最小到最大插损信道的情况:

针对最短校准通道和中间校准通道,RX只能使用一阶CTLE均衡;针对最长的校准通道,RX可以使用一阶CTLE均衡和1tap的DFE均衡。

其中CTLE均衡的传递函数:

Adc是指DC增益,协议规定可以在-6dB和-12dB之间以1dB的步长调节。曲线如下:

DFE均衡的框图如下:

DFE均衡的框图如下:

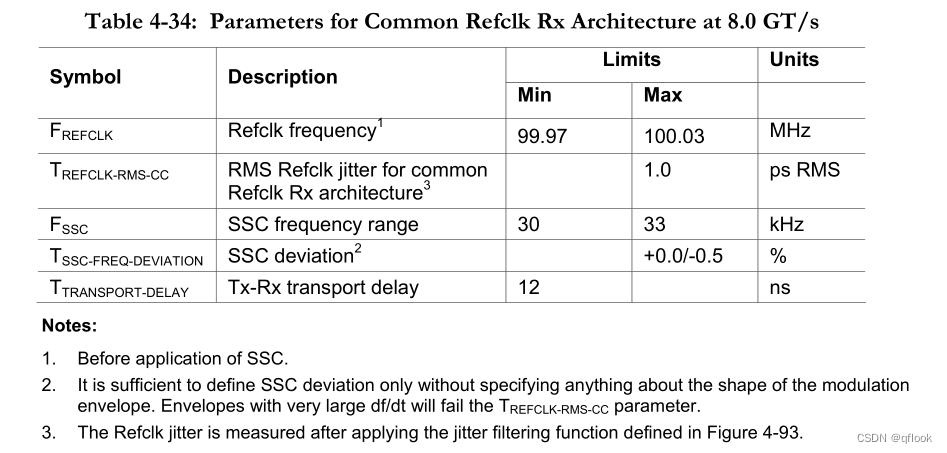

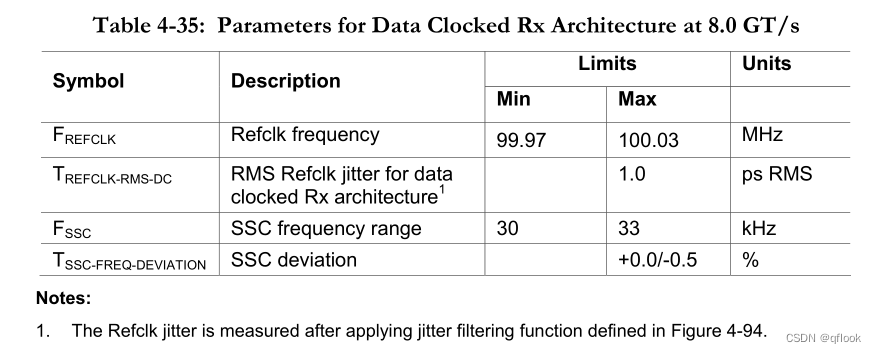

4)参考时钟

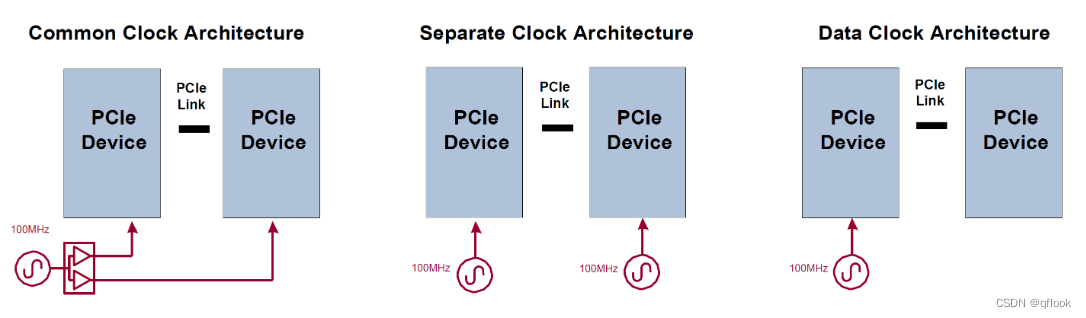

参考时钟Refclk的频率是100MHz,其功能不是数据时钟同步,而是给内部控制器的时钟。主要有三种模式:

共享参考时钟的具体参数要求如下:

共享参考时钟的具体参数要求如下:

嵌入式参考时钟参数要求:

独立的参考时钟要求就是两个时钟都是±300ppm。

三种参考时钟对比:

| 类型 | 优点 | 缺点 | 备注 |

| 共享参考时钟 | 1)收发侧的时钟抖动jitter都是相同的,因此便于跟踪和计算 2)低功耗模式仍然可用,防止PLL偏移 | 时钟偏差要控制在12ns以内,对比较大的板卡或跨板等情况的实现有很大挑战 | 稳定性好,应用最广泛 |

| 独立参考时钟 | 独立提供时钟,完全不受PCB布局、走线长度的影响 | 现在没有方案可以确定对端参考时钟是否开启SSC,影响抖动计算 | |

| 嵌入式参考时钟 | 实现简单 | PCIE4.0取消了本方案 | 不推荐 |

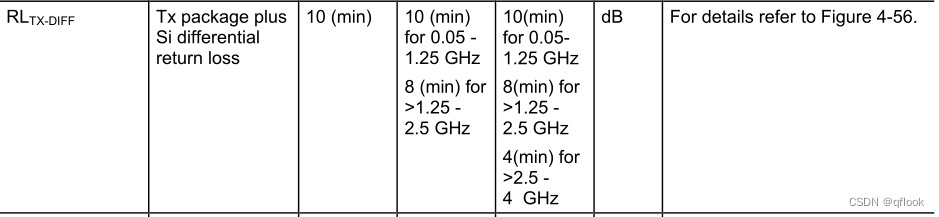

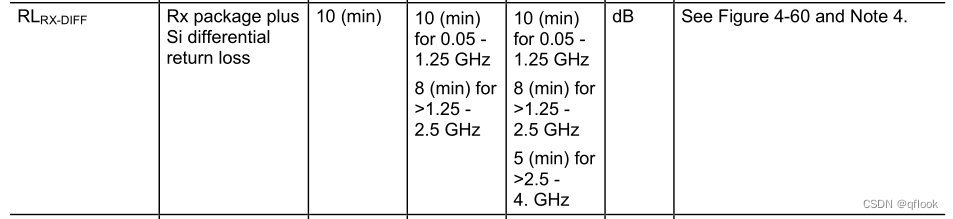

三、S参数要求

协议规定了芯片内的差分回损SDD11,具体如下:

具体大小如下参数要求:

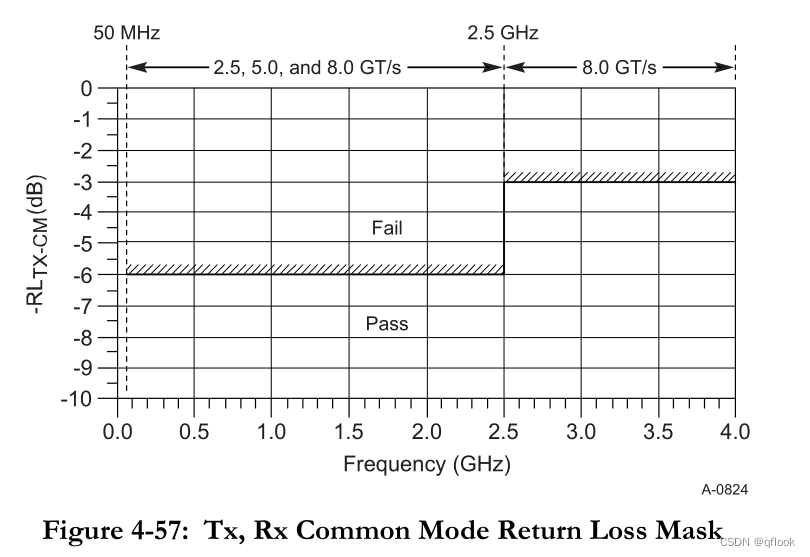

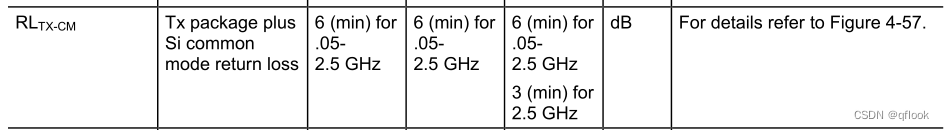

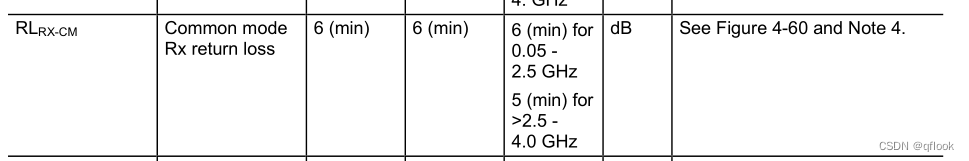

协议同样要求共模回损SCC11,具体如下:

协议同样要求共模回损SCC11,具体如下:

具体大小如下参数要求(注意RX的参数和图对应不上,不确定是图仅画出了TX没有包含RX,还是参数写错了):

测试方法也是通过疏导通道的SMA头连接网分进行,不过测试结果通过去嵌来排除疏导通道的影响。

测试方法也是通过疏导通道的SMA头连接网分进行,不过测试结果通过去嵌来排除疏导通道的影响。

原文地址:https://blog.csdn.net/qflook/article/details/138800274

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!