chapter 12 Bandgap References

chapter 12 Bandgap References

这一章我们介绍电压和电流基准. 首先学习和输入电压无关的偏置和起动问题. 然后介绍和温度有关的基准电压, 考虑offset对输出电压的影响. 最后学习恒定gm偏置和state-of-the-art电压基准.

12.1 General Considerations

一般基准电流有三种形式, 1) PTAT电流, 即电流大小和温度成正比. 2) constant Gm, 即管子的gm保持恒定. 3) bias不受温度影响.

12.2 Supply-Independent Biasing

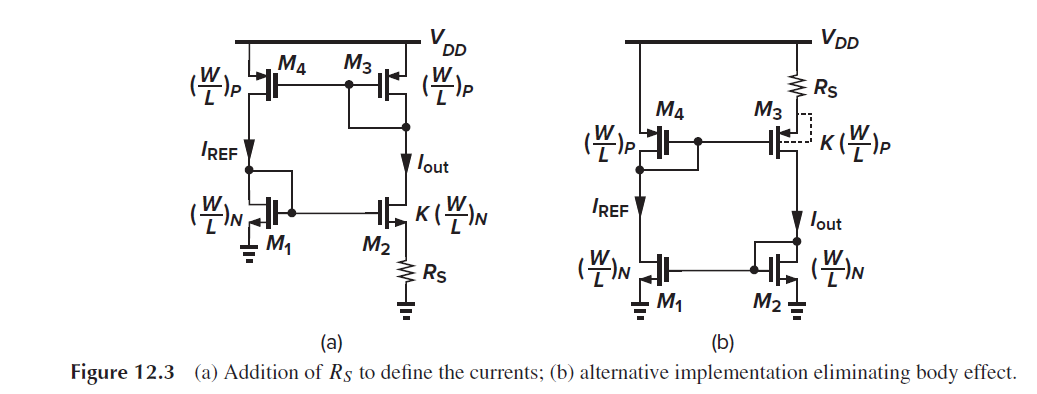

我们希望造出不随着输入电压VDD变化的电流, 而且Iref和Iout还能相互copy, 自己产生. 电路结构参考下图

Vgs1=Vgs2+ID2*Rs

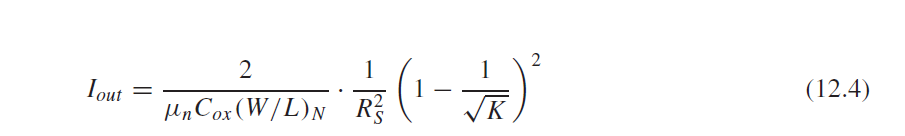

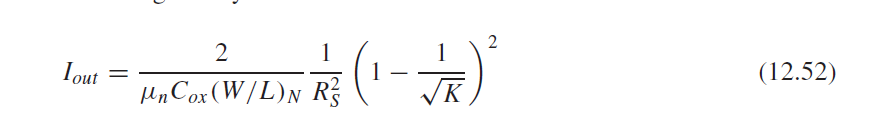

假设Vth1=Vht2, 忽略沟道调制效应, 可得 Iout表达式

Iout和1/Rs^2成正比, 作为MOS的偏置, gm=sqrt(Iout) 正比于1/Rs

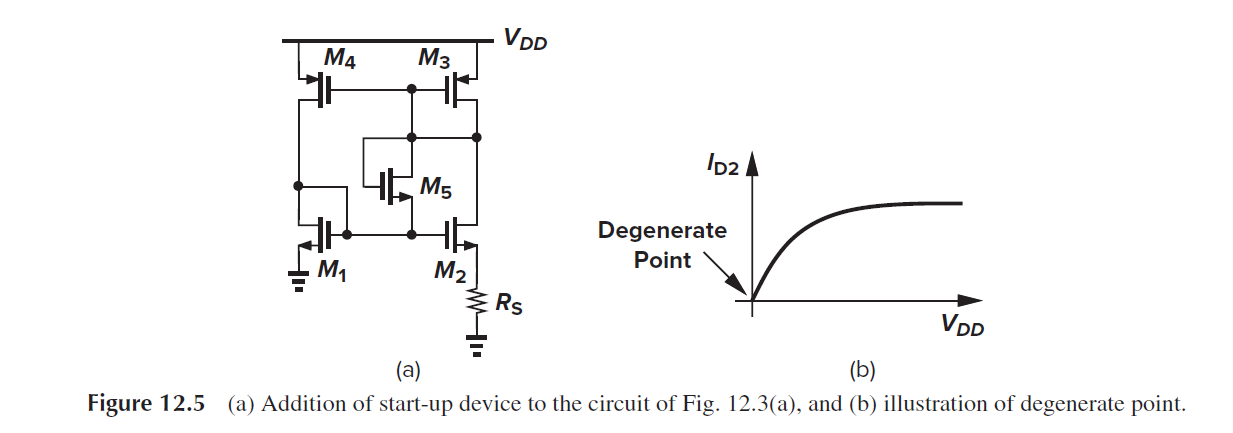

需要注意的是, 上面电路存在兼并点即degenerate bias point, 即电路可以工作在两种不同的工作模式, 即所有电流包括 Iout=0A.

解决办法是加入启动电路. 如下图M5. 检查兼并点问题, 需要用DC仿真, VDD从0V扫描到VDD. 确保Iout和VDD只有一个交点.

12.3 Temperature-Independent References

如何造一个恒温的bias呢? 我们可以用一个负温系数的+正温权重系数, 产生零温系数Zero temperature coefficients (TCs). 三极管是最佳产生正温度和负温度系数的器件.

12.3.1 Negative-TC Voltage

对于三极管, 其Vbe电压呈负温度系数, 在室温下, Vbe约等于0.7V.

∂

V

B

E

∂

T

=

−

1.9

m

V

/

K

\frac{\partial V_{BE}}{\partial T}=-1.9mV/K

∂T∂VBE=−1.9mV/K

12.3.2 Positive-TC Voltage

两个三极管工作在不同电流下, 电流比如为n, 那么Vbe的压差成正温度系数.

Δ

V

B

E

=

V

B

E

1

−

V

B

E

2

=

V

T

l

n

n

\Delta V_{BE}=V_{BE1}-V_{BE2}=V_Tlnn

ΔVBE=VBE1−VBE2=VTlnn

∂ Δ V B E ∂ T = k q l n n \frac{\partial \Delta V_{BE}}{\partial T}=\frac{k}{q}lnn ∂T∂ΔVBE=qklnn

Vbe差值的温度系数为0.087mV/K.

12.3.3 Bandgap Reference

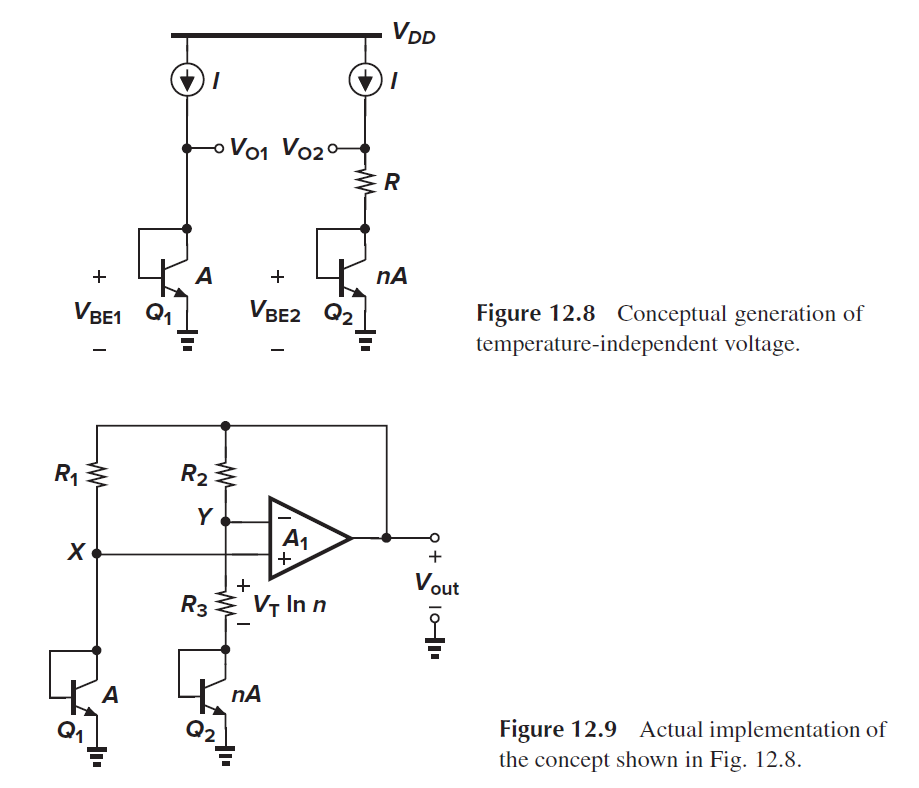

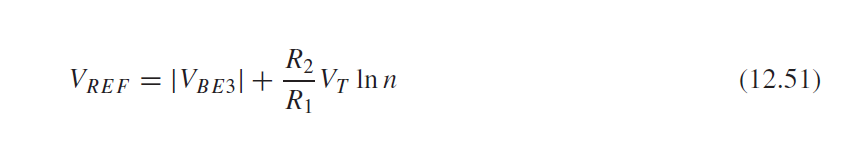

我们希望能建一个基准 VREF ≈ VBE + 17.2VT ≈ 1.25V, 这样就成零温漂. 考虑下图

钳位住Vo1=Vo2, 再加上电阻比例R2/R3, 可得输出Vout

V

o

u

t

=

V

B

E

2

+

V

T

ln

n

R

3

(

R

3

+

R

2

)

=

V

B

E

2

+

(

V

T

ln

n

)

(

1

+

R

2

R

3

)

V_{out}=V_{BE2}+\frac{V_T\text{ln}n}{R_3}(R_3+R_2)=V_{BE2}+(V_T\text{ln}n)(1+\frac{R_2}{R_3})

Vout=VBE2+R3VTlnn(R3+R2)=VBE2+(VTlnn)(1+R3R2)

为实现零温漂. (1 + R2/R3) ln n ≈ 17.2, 可取, n = 31, R2/R3 = 4.

Fig 12.9电路实际会遇到一些问题:

Collector Current Variation Vbe的温漂实际工艺会略大于−1.5 mV/K.

Compatibility with CMOS Technology pnp BJT需要和CMOS进行工艺兼容

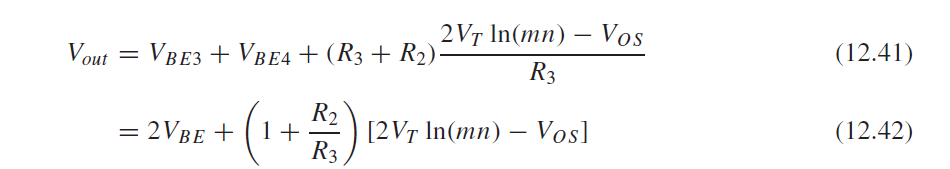

Op Amp Offset and Output Impedance: 考虑运放输入offset 为Vos

为了减小运放offset对于输出的影响, 1)可增加输入管子尺寸减少Vos. 2) Q1和Q2的电流可成M倍比例VBE = VT ln(mn), 3)可采用两级PN串联结构.

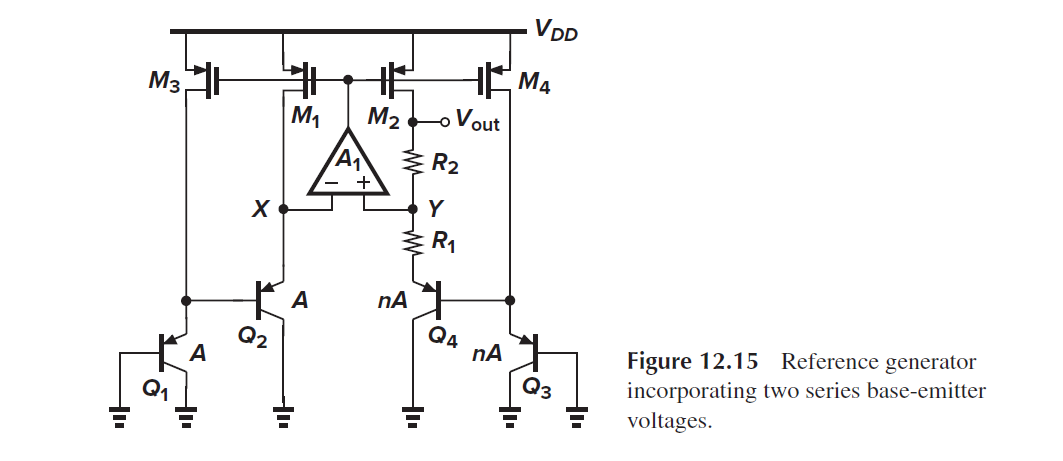

参考下图结构, 采用2) 和3) 项技术, 减少了R2/R3比例, 且增加了第一项, 减少了Vos对Vout的影响.

VBE1+VBE2−VOS = VBE3+VBE4+R3*I2

因此可得

Vout ≈ 2 × 1.25 V = 2.5 V

在老工艺实际电路中, collector可能需要接地, 可采用下图电路, 这样和串联BJT效果一样

Feedback Polarity

运放的极性很重要, 要确保负反馈的增益>正反馈增益, 系统才不会震荡

负反馈factor

正反馈factor

负反馈增益>正反馈增益, βP < βN 才能保证系统稳定

Supply Dependence and Start-Up

Fig 12.9电路需要启动电路, 确保Vx和Vy不为零. supply rejection取决于运放的VDD rejection性质.

Curvature Correction 在室温做完trim, Vref温度曲线可能成抛物线, 而且可工艺相关, CMOS比BJT更差.

12.4 PTAT Current Generation

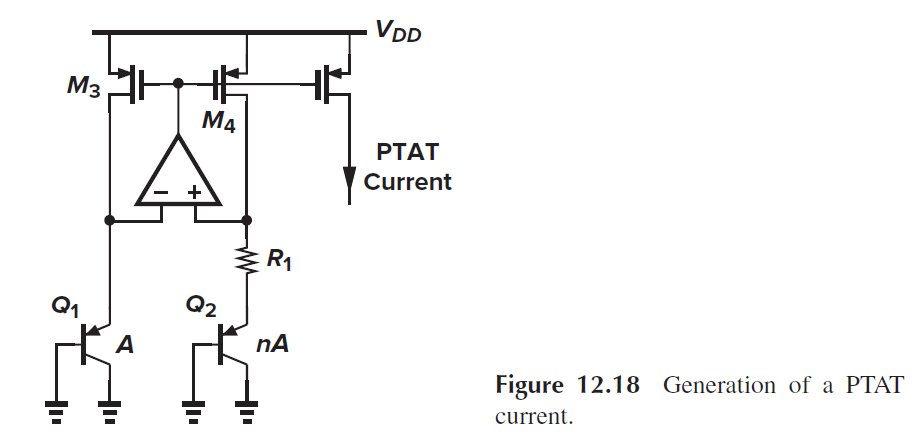

许多场景需要用到正温度系数PTAT电流, 可用上一节结构OP产生

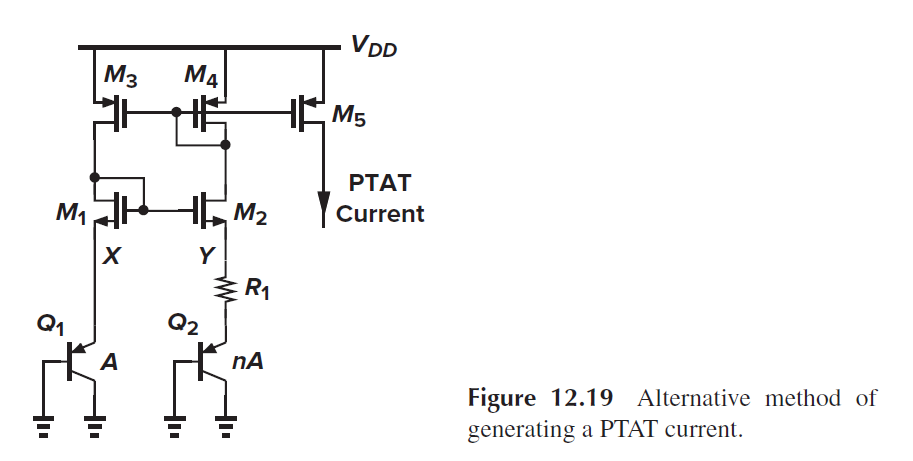

或者结合第二小节自我复制的结构如下: ID1=ID2. Vx=Vy. ID1 = ID2 = (VT ln n)/R1.

Fig12.18对于VDD的要求比Fig12.19低, 而且power rejection ratio要大一些. Fig12.18更适合低电压场景.

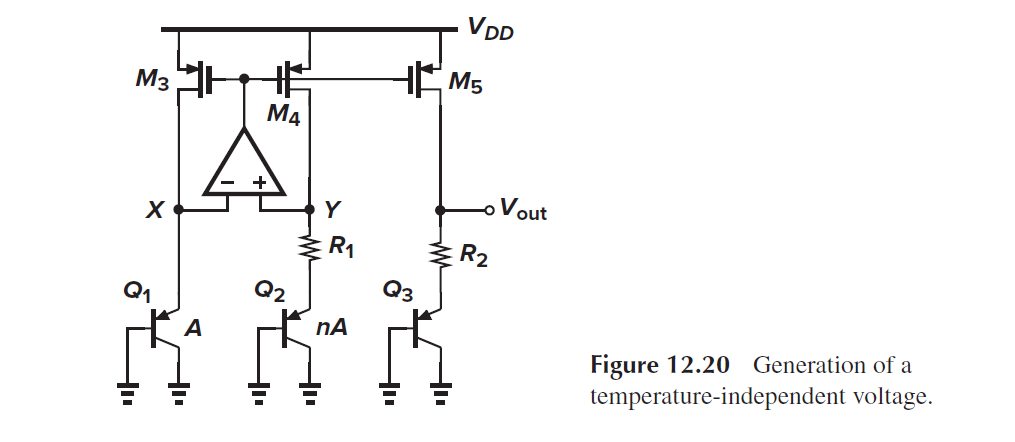

根据Fig12.18可得Fig 12.20结构的恒温Vref

ID5为PTAT电流, 叠加到Q3 Vbe上, 因此 Vout表达式为

实际电路中PMOS的mismatch会给Vout引入error.

12.5 Constant-Gm Biasing

MOS管的gm是一个重要参数, 决定了noise, 小信号增益和速度. 因此一些场景希望能把MOS的gm固定, 不受温度,工艺和供电电压的变化.

Fig 12.3就能产生constant gm电路

Iout和Rs^2成反比

因此M1的gm和Rs成反比, 与工艺无关.

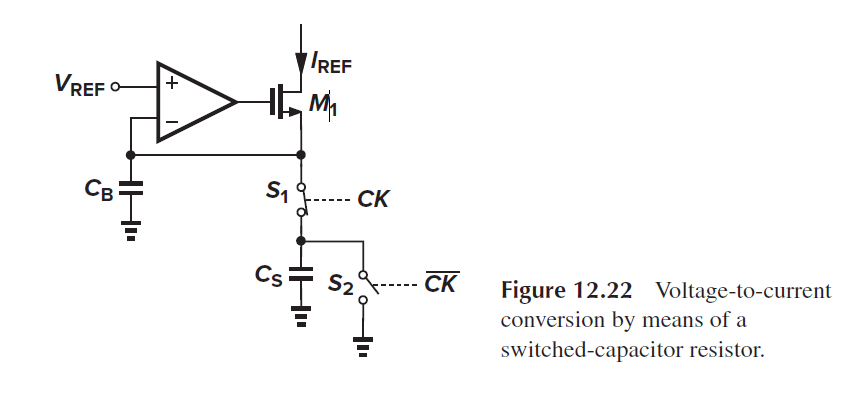

实际工艺中Rs受工艺和温度偏差很大. 可以用switched capacitor结构代替Rs, 如下图所示

R

s

=

1

C

s

f

C

K

R_{s}=\frac{1}{C_sf_{CK}}

Rs=CsfCK1

Cs和fck不随温度和工艺变化, 精度很高

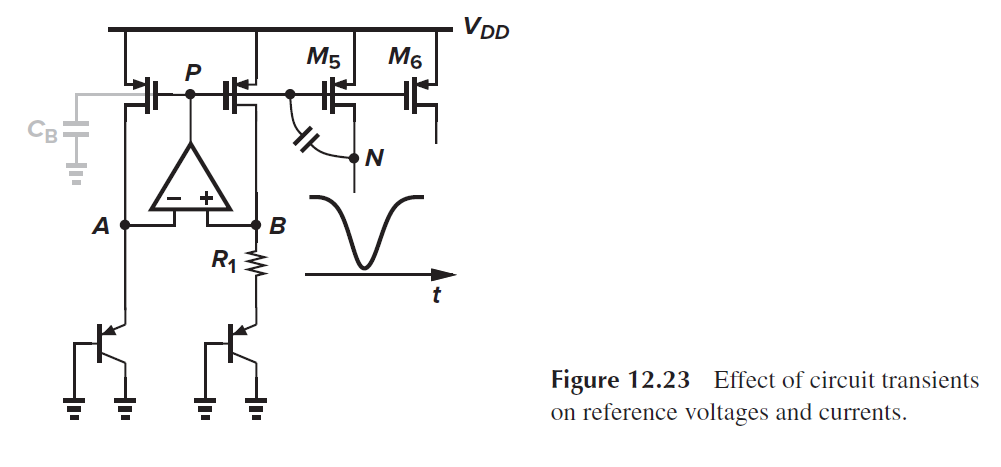

另外可以添加Cb来 short高频噪声 to ground, 如下图所示

12.6 Speed and Noise Issues

对于上图中的BG, P点通过M5容易受到N的串扰. 解决办法是增加Cb. 带来的issue是op-amp运放稳定性问题, 而且响应会变慢.

推导可得, 运放的的噪声直接体现在输出上. 添加Cb并不能抑制1/f 噪声.

12.7 Low-Voltage Bandgap References

bandgap电压大约为1.25V, 是因为需要凑出Vbe+17.2*Vt, 这样才能形成零温漂电压. 但是这限制了最低供电电压.

考虑下图

Vx=Vy, 当R2=R3, Ic1=Ic2. 因此Ic2为PTAT电流, IC2 = VT ln n/R1

流过R2的电流|VBE1| / R2为CTAT负温度系数电流. 因此ID4能产生零温漂电流:

因此输出Vbg为

V

B

G

=

R

4

R

2

(

V

B

E

1

+

R

2

R

1

V

T

l

n

n

)

V_{BG}=\frac{R_4}{R_2}\left( V_{BE1}+\frac{R_2}{R_1}V_T ln n \right)

VBG=R2R4(VBE1+R1R2VTlnn)

选择(R2/R1) ln n ≈ 17.2, 那么BG就能产生零温漂电压, 而且通过减小R4/R2, 输出能比1.25V低.

流过10uA电流, Q2 Vbe大约为0.7V, PMOS的Vds为50mV. 因此VDD最低可到0.75V.

R4为大电阻 (50Kohm), 会产生噪声而且输出需要bypass电容.

考虑Op-amp的offset VOS

增加N能减小运放Vos的影响.

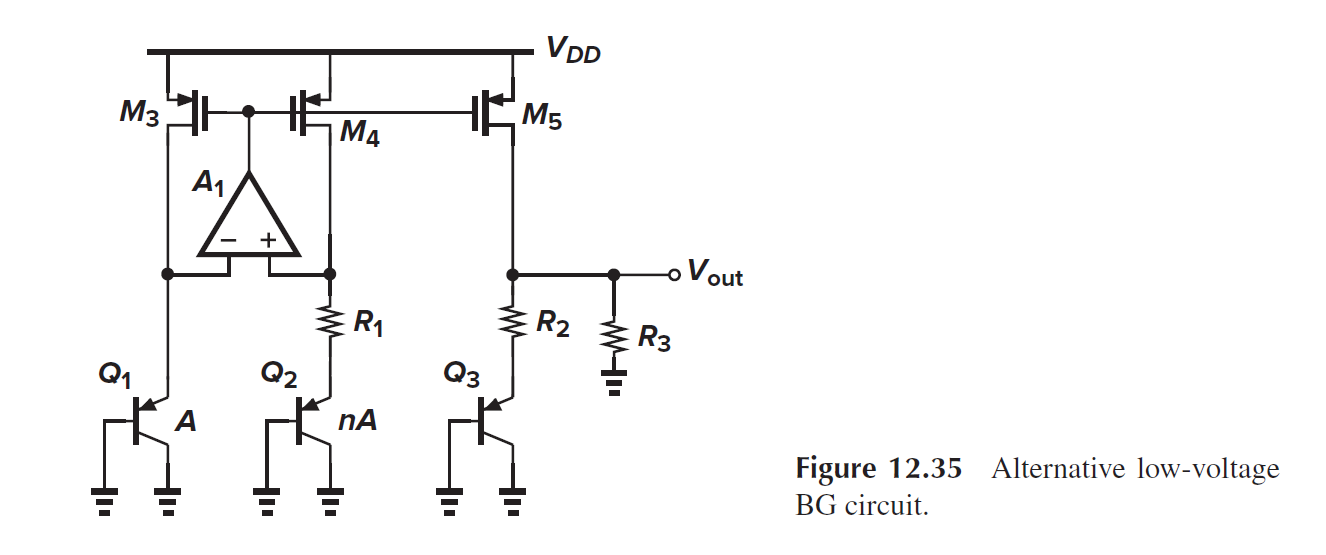

另外一种低电压BG电路如下

I

D

5

=

V

o

u

t

R

3

+

V

o

u

t

−

V

B

E

3

R

2

I_{D5}=\frac{V_{out}}{R_3}+\frac{V_{out}-V_{BE3}}{R_2}

ID5=R3Vout+R2Vout−VBE3

ID5=Vt lnn/R1, 为PTAT电流, 可得输出电压

V

o

u

t

=

R

3

R

2

+

R

3

(

V

B

E

3

+

R

2

R

1

V

T

ln

n

)

V_{out}=\frac{R_3}{R_2+R_3}\left( V_{BE3}+\frac{R_2}{R_1}V_T\text{ln}n \right)

Vout=R2+R3R3(VBE3+R1R2VTlnn)

输出电压被减小了R3/(R2+R3)倍.

12.8 Case Study

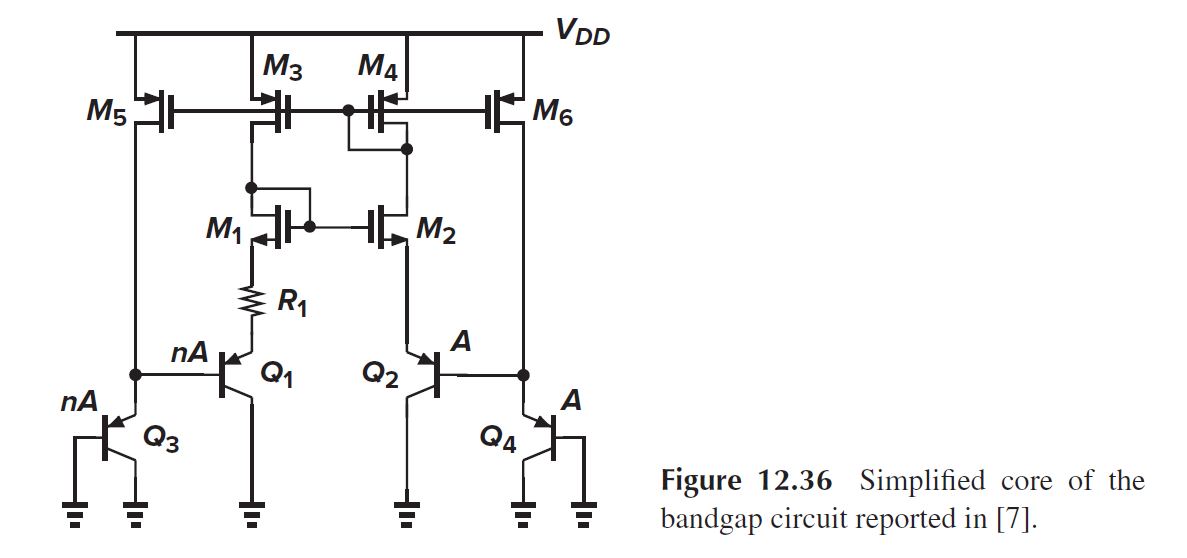

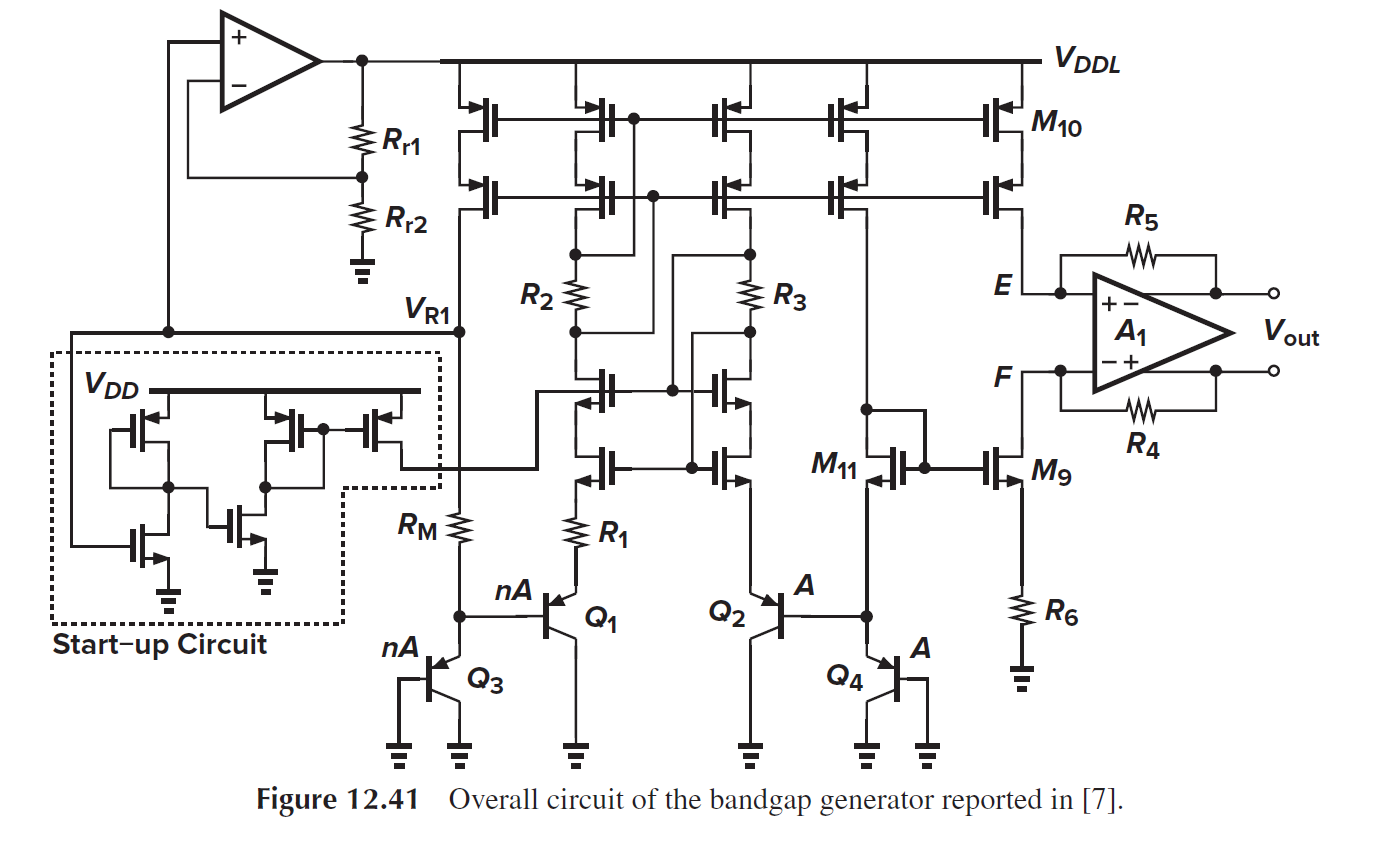

我们以下图BG为例

首先要解决Channel-length modulation 沟道调制效应, 可采用NMOS+PMOS cascode结构 替代M1/M2, M3/M4.

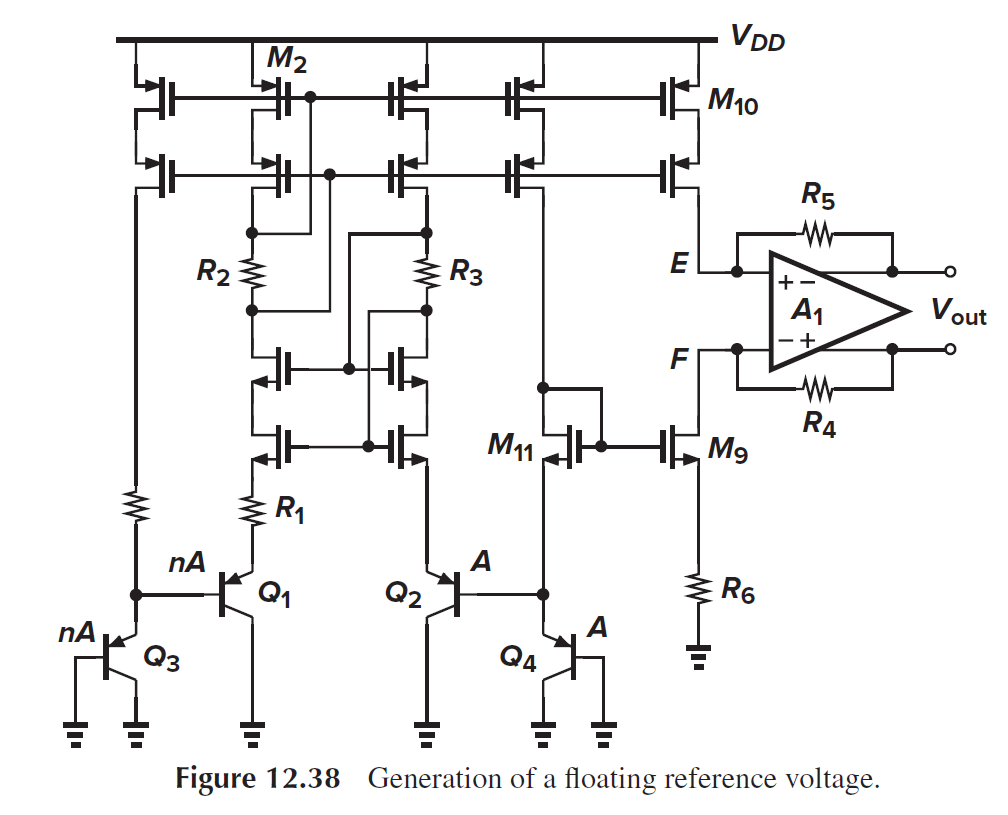

需要产生Vout, 浮动基准源

Vgs11=Vgs9, 因此R6上的电压为Vbe4, R4上的压降为Vbe4/R6*R4

M2和M10的尺寸一致, 因此ID10 = 2(VT ln n)/R1, 因此VR5 = 2(VT ln n)(R5/R1).

运放Ve=Vf, 因此输出Vout为VR4+VR5, 可产生零温漂电压

最终电路成这样

VDDL为产生的LDO电源, 为BG提供更好的PSRR. LDO的基准来自VR1, 通过RM电阻产生bandgap reference. 启动电路也包含.

原文地址:https://blog.csdn.net/2304_76736886/article/details/142445012

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!