时序深入之CPR(Clock Pessimism Removal)详解

目录

一、CPR概念

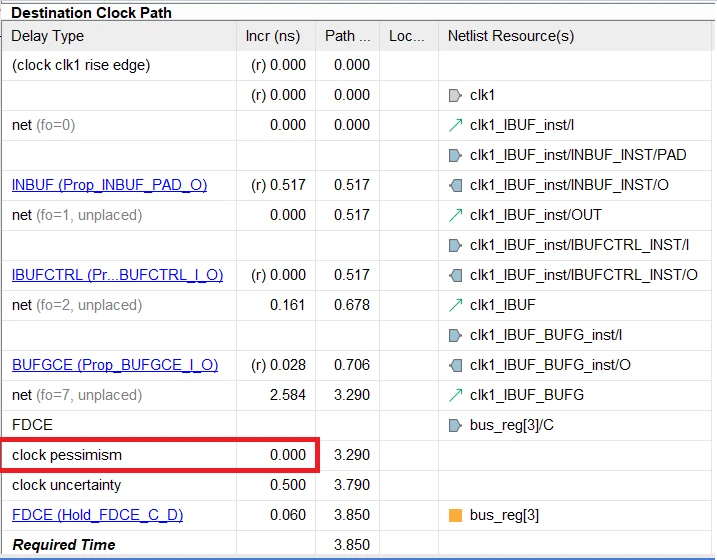

在时序报告的目标时钟路径中,会有一行数据clock pesssimism,第一次见可能都会对这个概念感到疑惑

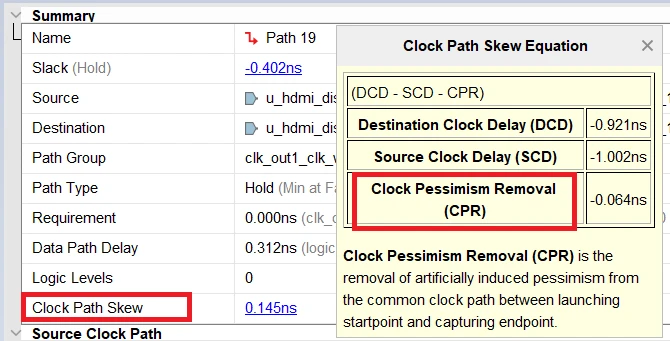

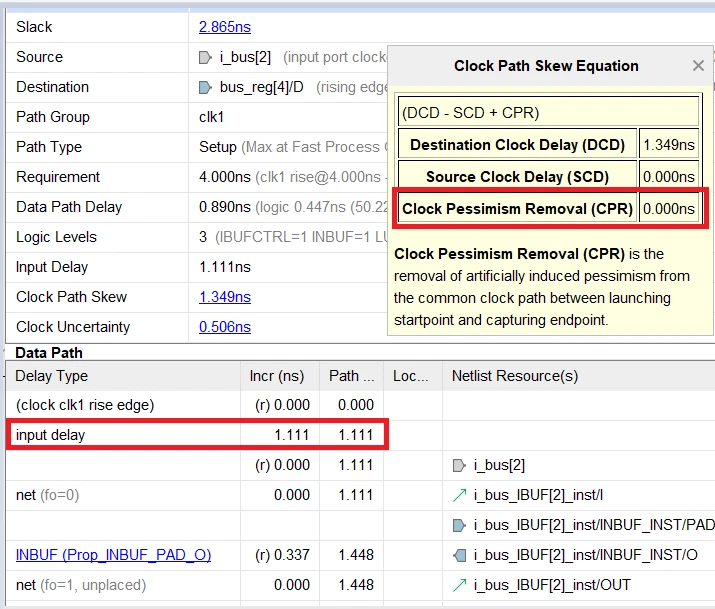

同样在每条时序路径的summary中,clock path skew的计算会出现CPR,根据下方的解释大意为CPR是人为从时序路径的起点和终点间的共同时钟路径移除悲观因素,看到这仍旧会满头问号

为了进一步详细的解释,以下面的官网图片来解释。REGA和REGB是由相同的时钟驱动,数据从REGA到REGB,还有下面几个概念需作为前提知识,

1)静态时序分析中,通常主要进行setup分析和hold分析,两种分析本质是比较时钟路径和数据路径的时延,但时钟路径和数据路径在FPGA的时延是一个和工艺,电压,温度有关的概率时延,即同一段路径的时延值不是完全的固定值。

2)通常环境由两种极端环境情况,最好fast和最差slow,每种情况下的信号时延(包括时钟信号和数据信号)又存在最大值和最小值。

3)对于setup最差的情况分析,则采用数据时延最大,时钟时延最小的场景来分析。

回到下图中,时钟路径中,最前面一段加粗的是源时钟路径与目的时钟路径共同的部分,根据上面的第3条,上面的路径(红色)采用最大时延即Max Delay,时钟路径用最小时延(淡蓝色)Min Delay,这时计算REGB上的setup分析时,

数据路径时延Td=Max(Tsource_clk+Tckq+Tdata)

时钟路径时延Tclk=Min(Tdestination_clk)

setup=Tclk-Td=Min(Tdestination_clk)-Max(Tsource_clk)-Max(Tckq+Tdata)

对于Min(Tdestination_clk)-Max(Tsource_clk),仔细看下图中加粗的一段Destination clock和Source clock共同部分可知,同一个时钟同一段路径同一时刻是不可能出现一个最大时延和一个最小时延的,换句话说可以理解,对于共同的部分Min(Tdestination_clk)等于Max(Tsource_clk)。但如果这一段仍按照最大时延和最小时延来计算,则最终计算的setup值非准确值,因为,引入CPR来校正引入的误差,CPR的值为源时钟与目的时钟共同段的Max(Tsource_clk)-Min(Tdestination_clk)

二、CPR的计算

在目标时钟路径中,延时应该加上还是减去CPR值取决于分析的类型,对于最大时延分析,如setup/recovery分析,则是加上CPR,对于最小时延分析,如hold/removal分析,则是减去CPR值。

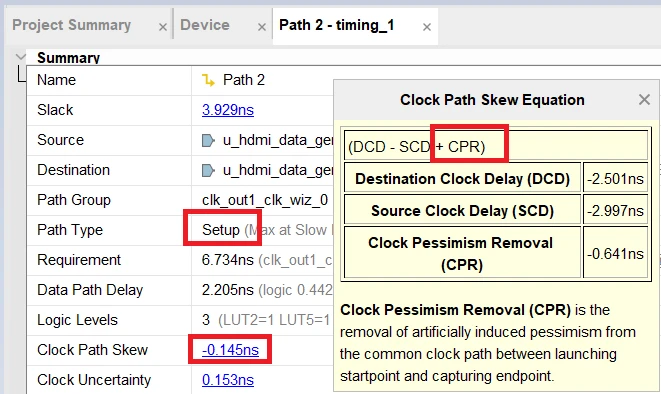

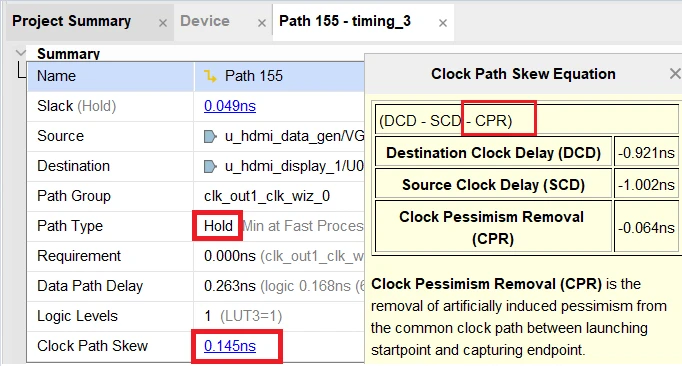

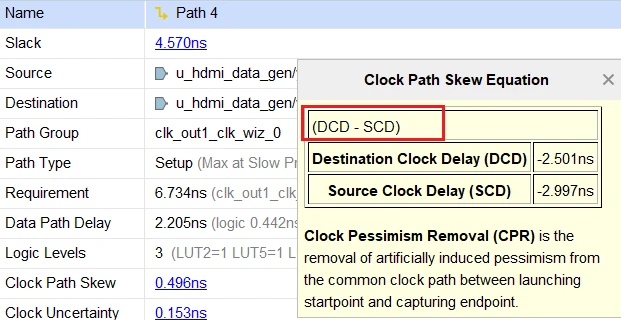

在每条时序路径的summary中,clock path skew由DCD,SCD和CPR决定,DCD为目的时钟延时,SCD为源时钟延时,CPR的作用如下图。

setup分析

hold分析

在很多设计中,CPR的精度在布线前后是不一样的。例如,假设起点和终点的时钟引脚是由相同的时钟BUFFER驱动,在布线前,共同的部分是时钟网线驱动源,即时钟BUFFER的输出引脚,CPR仅仅补偿从时钟根到时钟BUFFER输出引脚的差异。但在布线后,共同点的分叉位置是源时钟和目的时钟共享的最后一段布线资源,此时,共同的分叉点不能用网表来表现了,因此,CPR不能通过减去共有的时钟电路的延时差异。时序分析工具计算基于器件信息的CPR值也是不会直接呈现给用户。

三、CPR的开启关闭

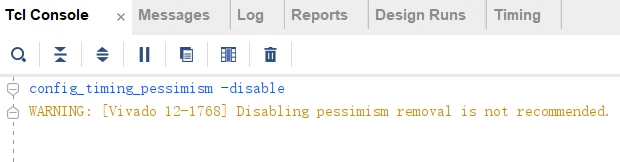

CPR可以设置打开或关闭,默认打开,不建议关闭,关闭后会导致时序分析不准,如果需要关闭,在tcl console执行命令config_timing_pessimism -disable

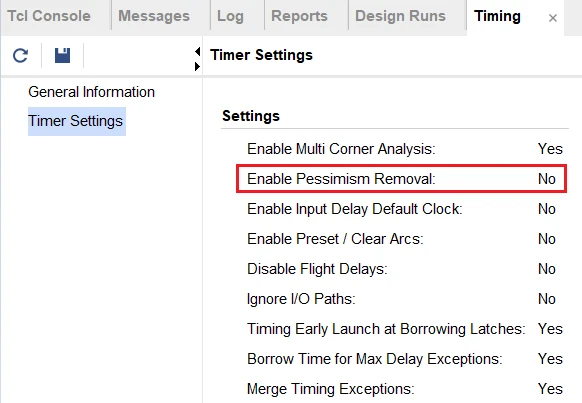

查看是否关闭成功,tcl窗口执行命令report_config_timing -name config,其中config为自定义的报告名称,enable pessimism removal的值为no表示关闭

此时,查看时序路径的clock path skew中已经没有CPR

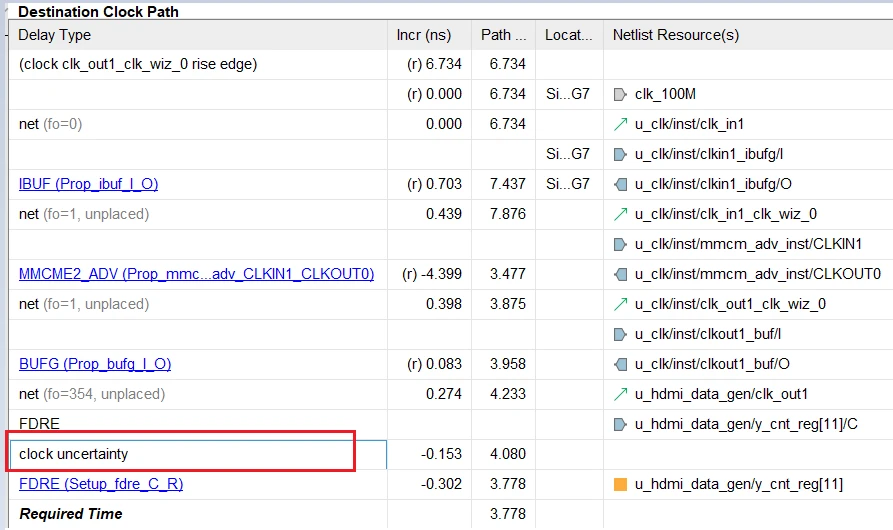

在destination clock path中,在路径的最后也不会计算clock pessimism

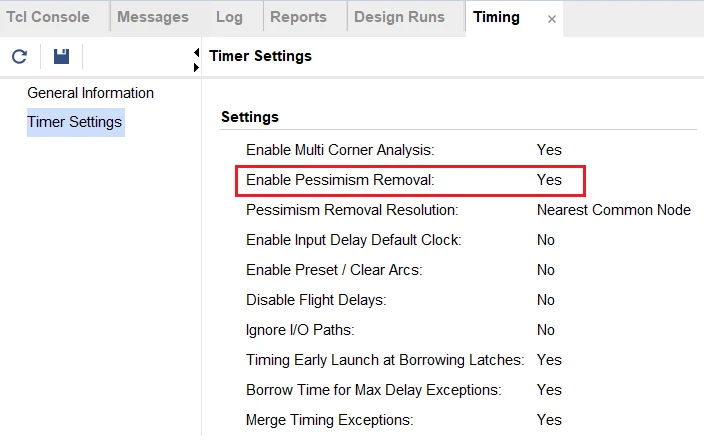

要打开则执行config_timing_pessimism -enable后查看信息,值为YES,说明打开成功

四、CPR为0

上面提到CPR是为解决源时钟和目的时钟在计算公共路径段引入的时延误差,但有时会发现时序路径上存在clock pessimism,但值为0的特殊场景。

不难理解,即源时钟和目的时钟的公共路径在setup/hold分析不会有误差,换句话说,就是没有公共部分。此处示例是因为设置了set_input_delay,分析的是输入端口到第一级触发器的时序,因为data path中是没有时钟的,无源时钟。

五、参考资料

《ug906-vivado-design-analysis-en-us-2023.2.pdf》

原文地址:https://blog.csdn.net/zyp626/article/details/137159054

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!