Vitis HLS 学习笔记--ap_int.h / ap_fixed.h(1)

目录

目录

1. 概述

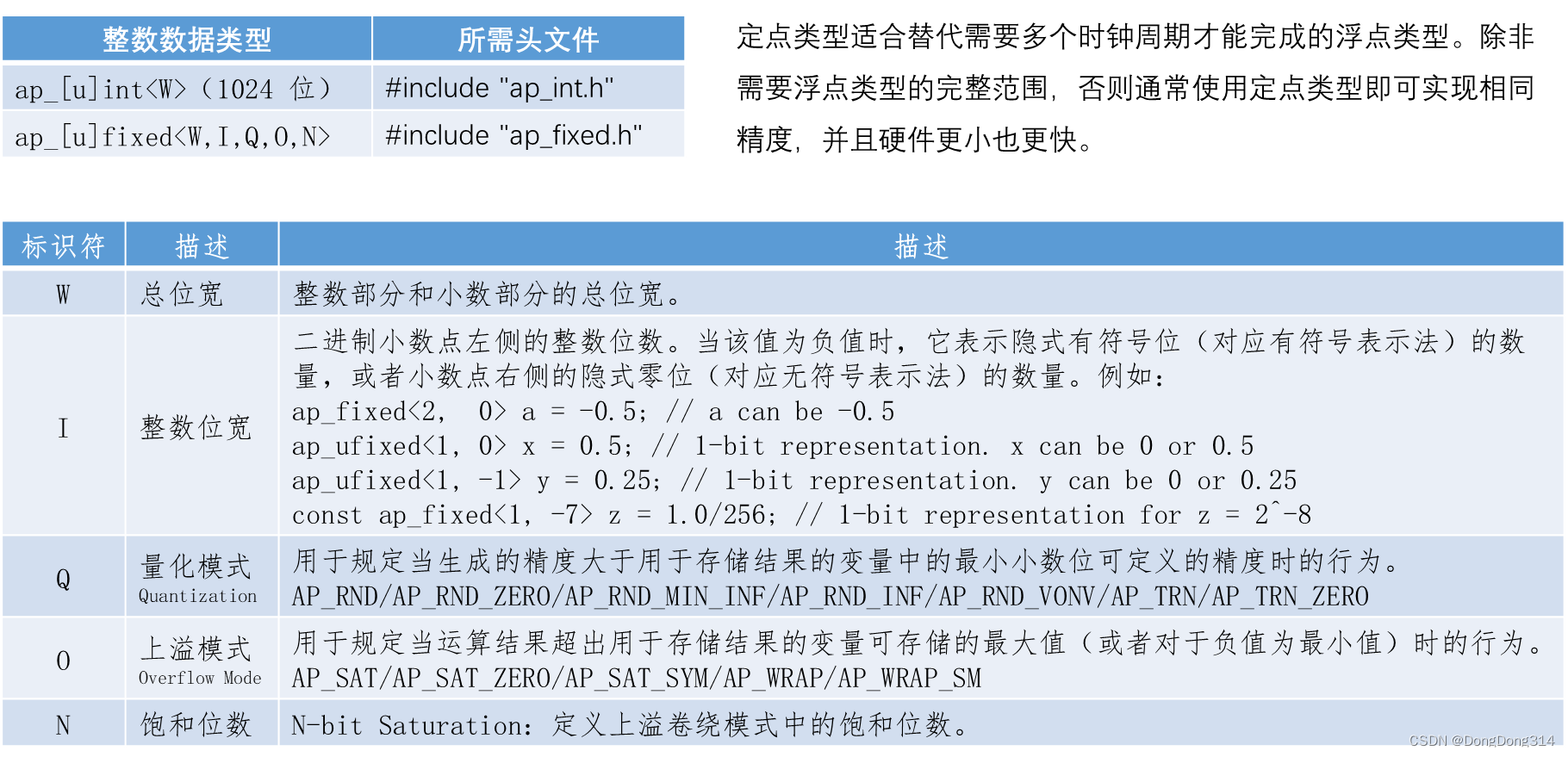

ap_int.h 和 ap_fixed.h 是 Vitis HLS (High-Level Synthesis) 工具中提供的两个非常重要的头文件,它们定义了一系列特殊的数据类型。

在 FPGA 设计中,资源是有限的,包括逻辑单元、存储单元和信号处理单元等。使用标准的数据类型(如 int、float 等)往往会导致资源浪费,因为这些类型的位宽是固定的,可能远远超过实际需求。ap_int.h 和 ap_fixed.h 提供的数据类型允许设计者精确地指定数据的位宽,从而实现资源的精细管理和优化。这种优化可以显著提高芯片的性能,降低功耗,减少成本。

通过精确控制数据位宽,可以减少不必要的数据操作和存储,从而减少逻辑延迟,提高数据处理速度。例如,在执行加法操作时,较小的数据位宽意味着较少的逻辑门延迟,从而加快运算速度。此外,较小的数据位宽还可以减少数据传输的带宽需求,提高整体系统的性能。

2. 简要规则

3. 浮点运算的复杂性

浮点运算单元(FPU)的设计比定点运算单元复杂得多,需要更多的逻辑电路和更多的时钟周期来完成一个运算。

浮点数通常遵循 IEEE 754 标准,该标准定义了浮点数的表示方式以及运算规则。一个浮点数由三个部分组成:符号位(表示正负)、指数位和尾数位(或称为有效数字)。这种表示方式使得浮点数能够表示极广泛的数值范围,但同时也带来了运算的复杂性:

2.1 对阶

在执行加法或减法运算时,两个浮点数的指数可能不同,需要进行对阶操作,即调整两个数的指数使其相同,然后才能对尾数进行加减操作。这个过程可能涉及尾数的右移操作,以及对溢出或下溢的处理。

3.2 尾数运算

一旦完成对阶,就可以对尾数进行加减或乘除运算。由于尾数通常包括一个隐含的最高位(对于规格化数),因此尾数运算比整数运算更为复杂。加上需要处理舍入和精度损失的问题,尾数运算需要额外的逻辑和时间。

3.3 规格化和舍入

运算结果可能需要规格化处理,以确保其格式符合浮点数的表示要求。规格化可能需要对尾数进行左移或右移,并相应地调整指数。此外,还需要进行舍入操作,以确保结果符合指定的精度要求。舍入操作本身就有多种模式(如向最近偶数舍入、向零舍入等),这增加了运算的复杂性。

3.4 特殊值的处理

浮点数表示还包括特殊值,如正无穷、负无穷和 NaN(非数)。在运算过程中需要检测和处理这些特殊值,这也是浮点运算复杂性的一个方面。

4. 示例(ap_fixed.h)

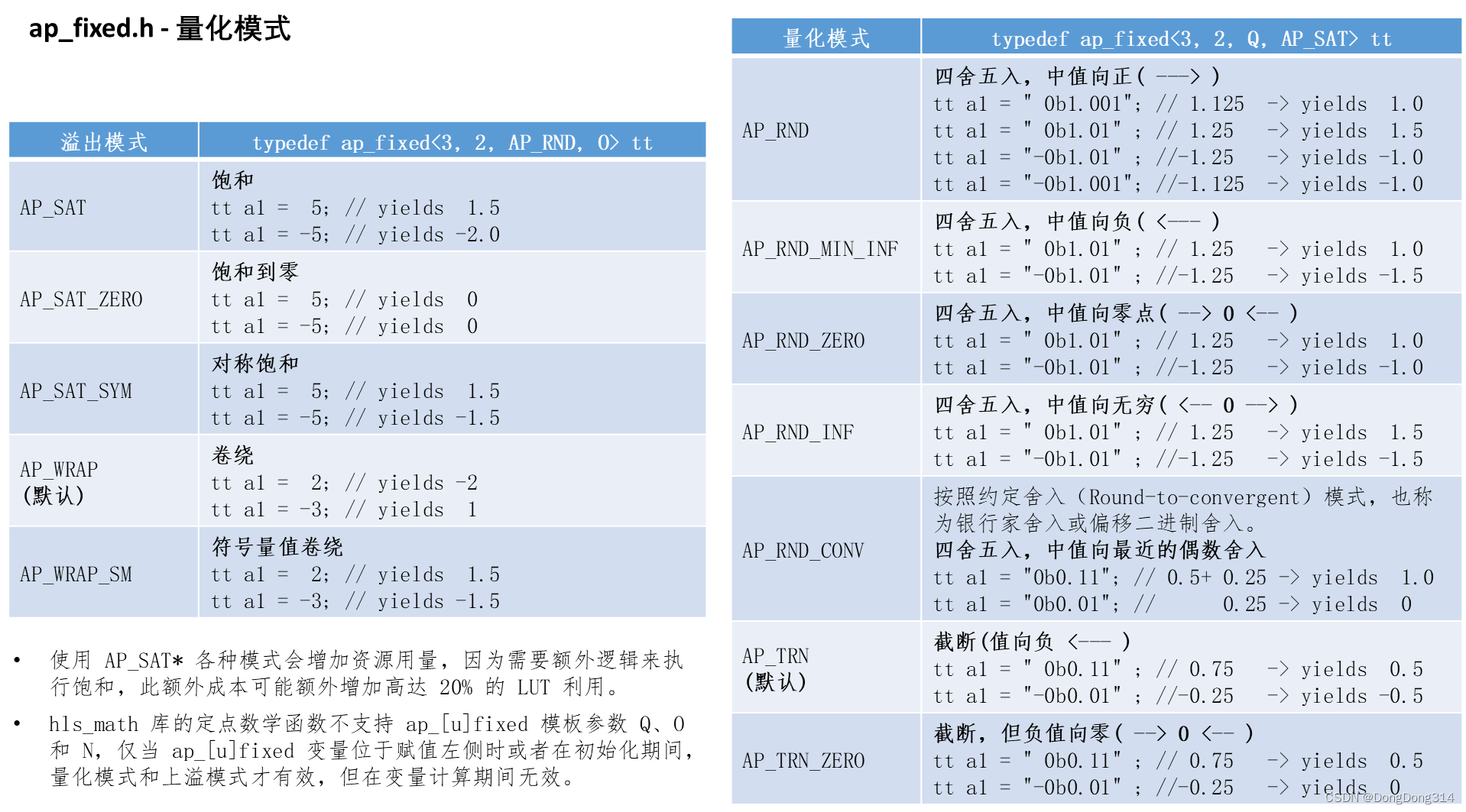

5. 量化模式(ap_fixed.h)

5.1 AP_SAT* 模式会增加资源用量

饱和算术运算需要检测运算结果是否超出了数据类型所能表示的最大或最小值。如果超出了,结果需要被设置为该数据类型能表示的最大值或最小值。这种检测和修正过程涉及到额外的比较、条件判断和赋值操作,从而需要更多的逻辑资源来实现。

原文地址:https://blog.csdn.net/DongDong314/article/details/137524952

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!