低密度奇偶校验码LDPC(九)——QC-LDPC译码器FPGA全并行设计

往期博文

低密度奇偶校验码LDPC(一)——概述_什么是gallager构造-CSDN博客

低密度奇偶校验码LDPC(二)——LDPC编码方法-CSDN博客

低密度奇偶校验码LDPC(三)——QC-LDPC码概述-CSDN博客

低密度奇偶校验码LDPC(四)——双对角线结构的QC-LDPC编码-CSDN博客

低密度奇偶校验码LDPC(五)——译码算法概述-CSDN博客

低密度奇偶校验码LDPC(六)——SPA和积译码算法-CSDN博客

低密度奇偶校验码LDPC(七)——SPA和积译码算法的简化-CSDN博客

低密度奇偶校验码LDPC(八)——QC-LDPC译码器FPGA设计概要-CSDN博客

QC-LDPC的FPGA实现

基于QC-LDPC编码的循环移位网络的FPGA实现_5g ldpc编码 桶形移位寄存器-CSDN博客

一、全并行算法(NMS译码算法)

二、实例分析

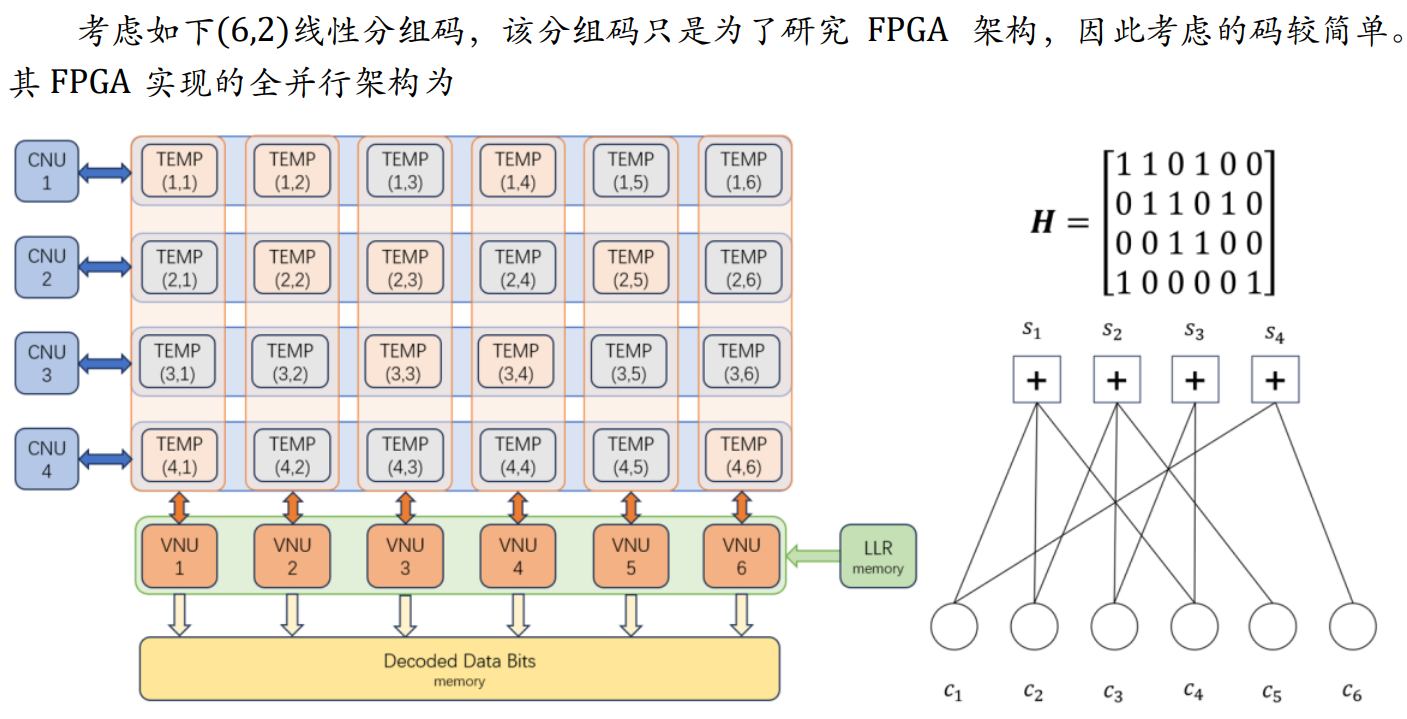

总体架构

CNU模块

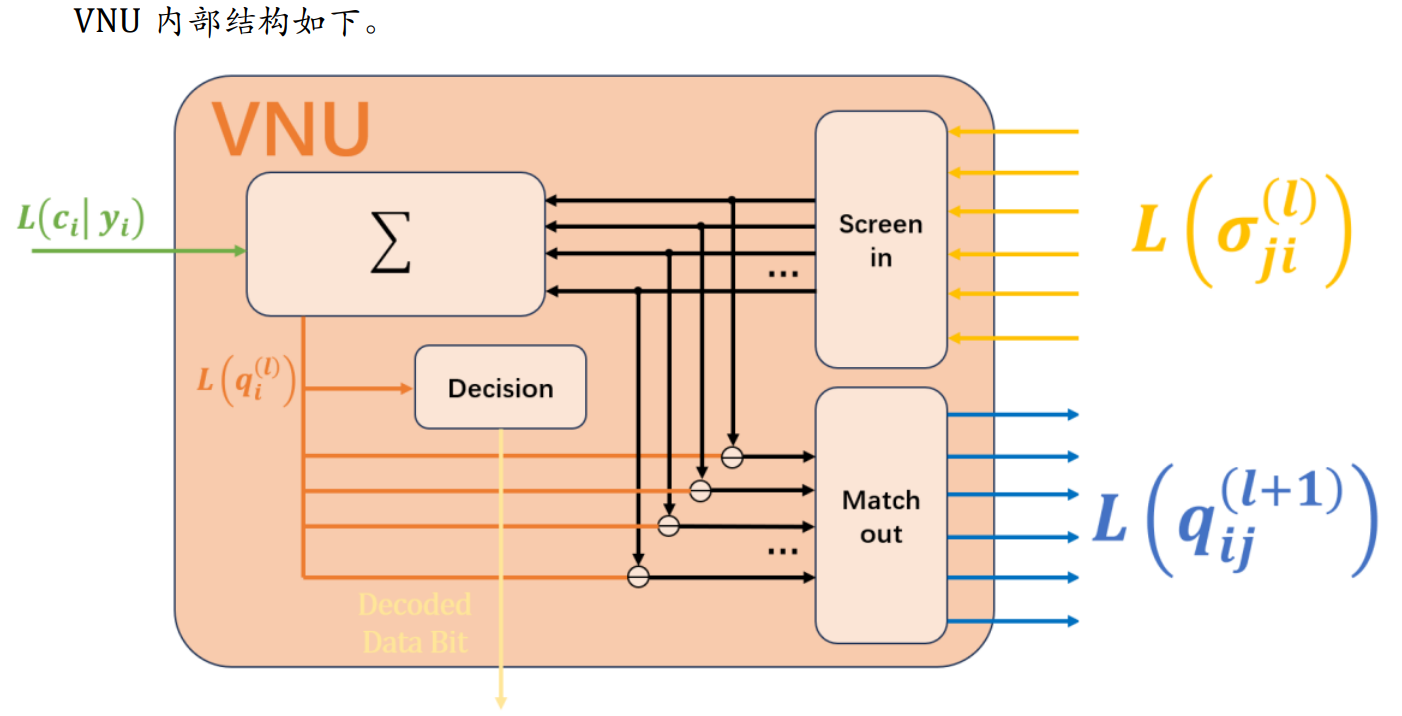

VNU模块

参考文献

[1] 白宝明 孙韶辉 王加庆. 5G 移动通信中的信道编码[M]. 北京: 电子工业出版社, 2018.

[2] William E. Ryan, Shu Lin. Channel Codes - Classical and Modern[M]. Cambridge University Press, 2009.

[3] Roth C, Cevrero A, Studer C, et al. Area, throughput, and energy-efficiency trade-offs in the VLSI implementation of LDPC decoders[C]// IEEE International Symposium of Circuits and Systems (ISCAS). 2011: 1772-1775.

[4] Zhongfeng Wang, Zhiqiang Cui, and Jin Sha. VLSI Design for Low-Density Parity-Check Code Decoding. IEEE CIRCUITS AND SYSTEMS MAGAZINE.2011

原文地址:https://blog.csdn.net/qq_63612412/article/details/136464678

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!