Verilog语法——按位取反“~“和位宽扩展的优先级

前言

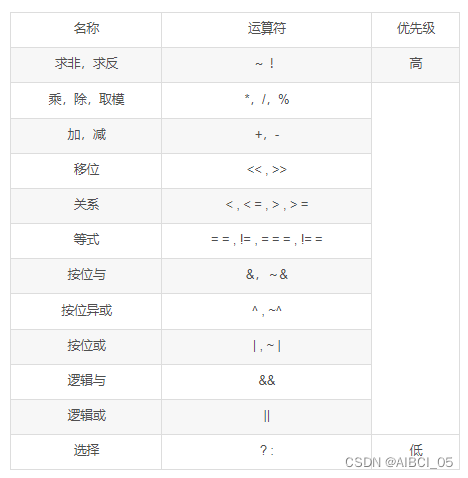

先说结论,如下图所示,在Verilog中“~ ”按位取反的优先级是最高的,但是在等式计算时,有时候会遇到位宽扩展,此时需要注意的是位宽扩展的优先级高于“~”。

验证

仿真代码,下面代码验证的是“~”按位取反和符号扩展的优先级。

module tb();

reg [7:0] a;

reg b;

wire [7:0] b1;

wire [7:0] b2;

wire [7:0] b3;

initial begin

a=0;b=0;

repeat(10)begin

#10

a={$random}%256;

b={$random}%2;

end

end

assign b1=a+~b;

assign b2=a+~{7'b0,b};

assign b3=a+{~b};

endmodule

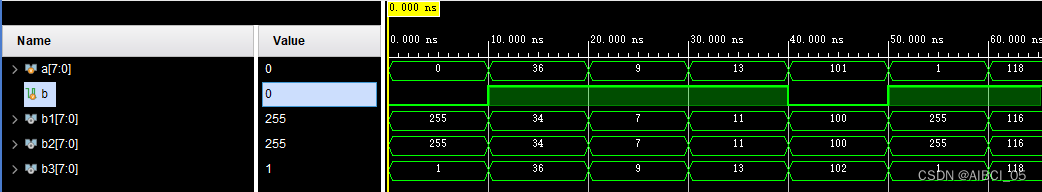

仿真结果

如上所示,b1=a+ ~ b相当于b2=a+ ~ {7’b0,b}$,但是实际应该是按照逻辑b3=a+{~ b}或者是b2=a+{ 7’b0,~ b }逻辑才对。

原文地址:https://blog.csdn.net/weixin_51116586/article/details/137527407

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!