16.分频器设计—奇分频

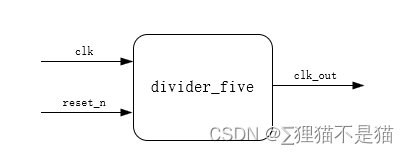

(1)Visio视图:

(2)Verilog代码:

module divider_five(clk,reset_n,clk_out);

input clk;

input reset_n;

output clk_out;

reg [2:0]cnt;

reg clk_1;

reg clk_2;

//计数器模块设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

cnt <= 3'd0;

else if(cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 3'd1;

//clk_1信号设计

always@(posedge clk or negedge reset_n)

if(!reset_n)

clk_1 <= 1'd0;

else if(cnt == 3'd2)

clk_1 <= 1'd1;

else if(cnt == 3'd4)

clk_1 <= 1'd0;

else

clk_1 <= clk_1;

//clk_2信号设计

always@(negedge clk or negedge reset_n)

if(!reset_n)

clk_2 <= 1'd0;

else if(cnt == 3'd2)

clk_2 <= 1'd1;

else if(cnt == 3'd4)

clk_2 <= 1'd0;

else

clk_2 <= clk_2;

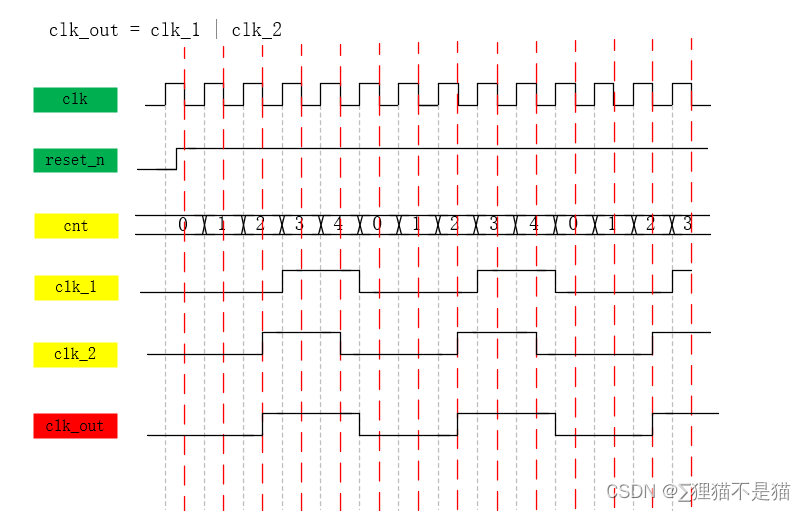

assign clk_out = (clk_1 | clk_2);

endmodule

(3)RTL视图:

(4)仿真文件代码:

`timescale 1ns / 1ps

module divider_five_tb;

reg clk;

reg reset_n;

wire clk_out;

divider_five divider_five_inst(

.clk(clk),

.reset_n(reset_n),

.clk_out(clk_out)

);

initial clk = 1'd1;

always #10 clk = ~clk;

initial begin

reset_n = 1'd0;

#20;

reset_n = 1'd1;

#2000

$stop;

end

endmodule

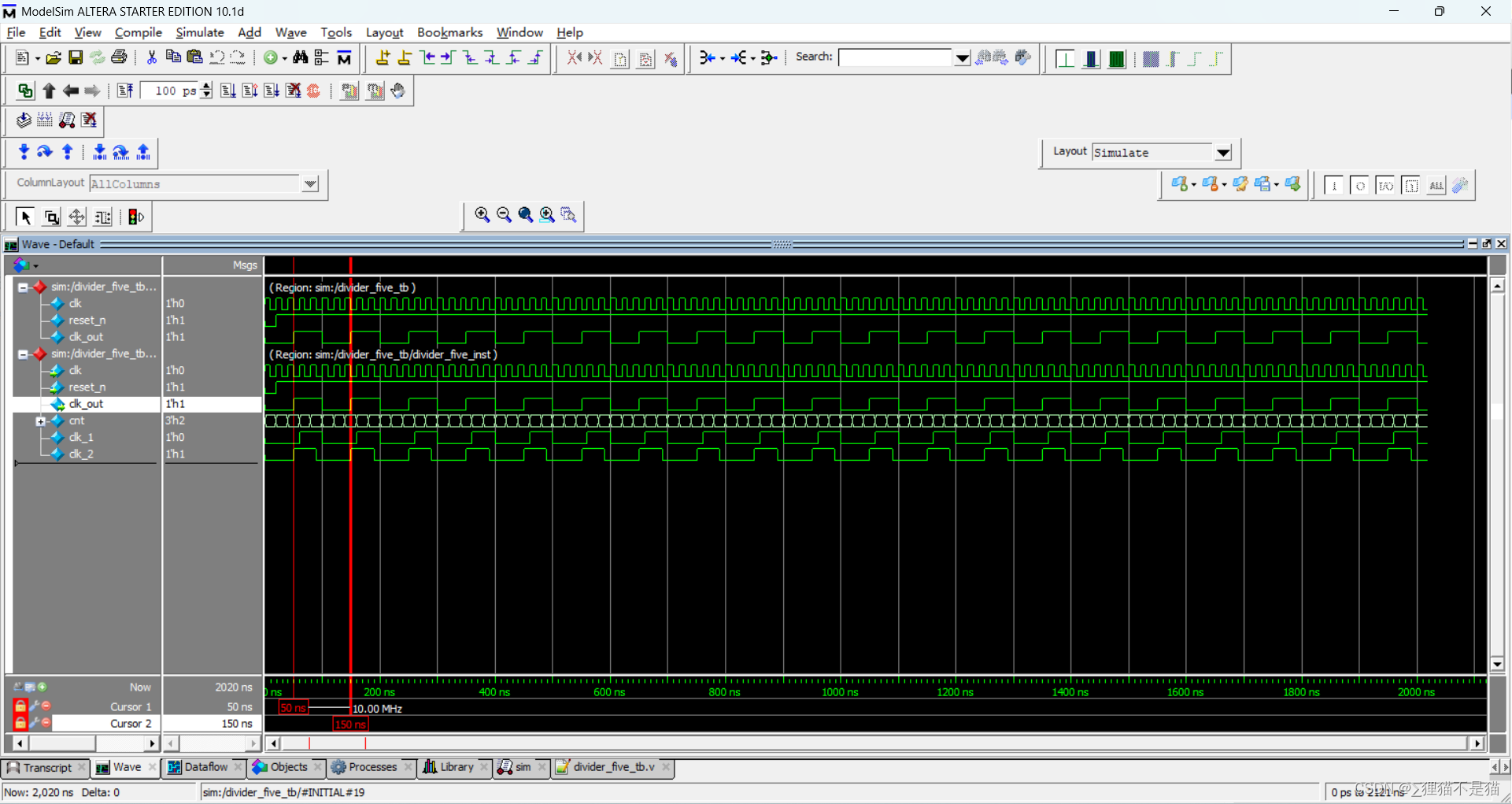

(5)仿真波形:

(6)引脚绑定:

set_property IOSTANDARD LVCMOS33 [get_ports clk_out]

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property PACKAGE_PIN M13 [get_ports clk_out]

set_property PACKAGE_PIN N15 [get_ports reset_n]

set_property PACKAGE_PIN W19 [get_ports clk]

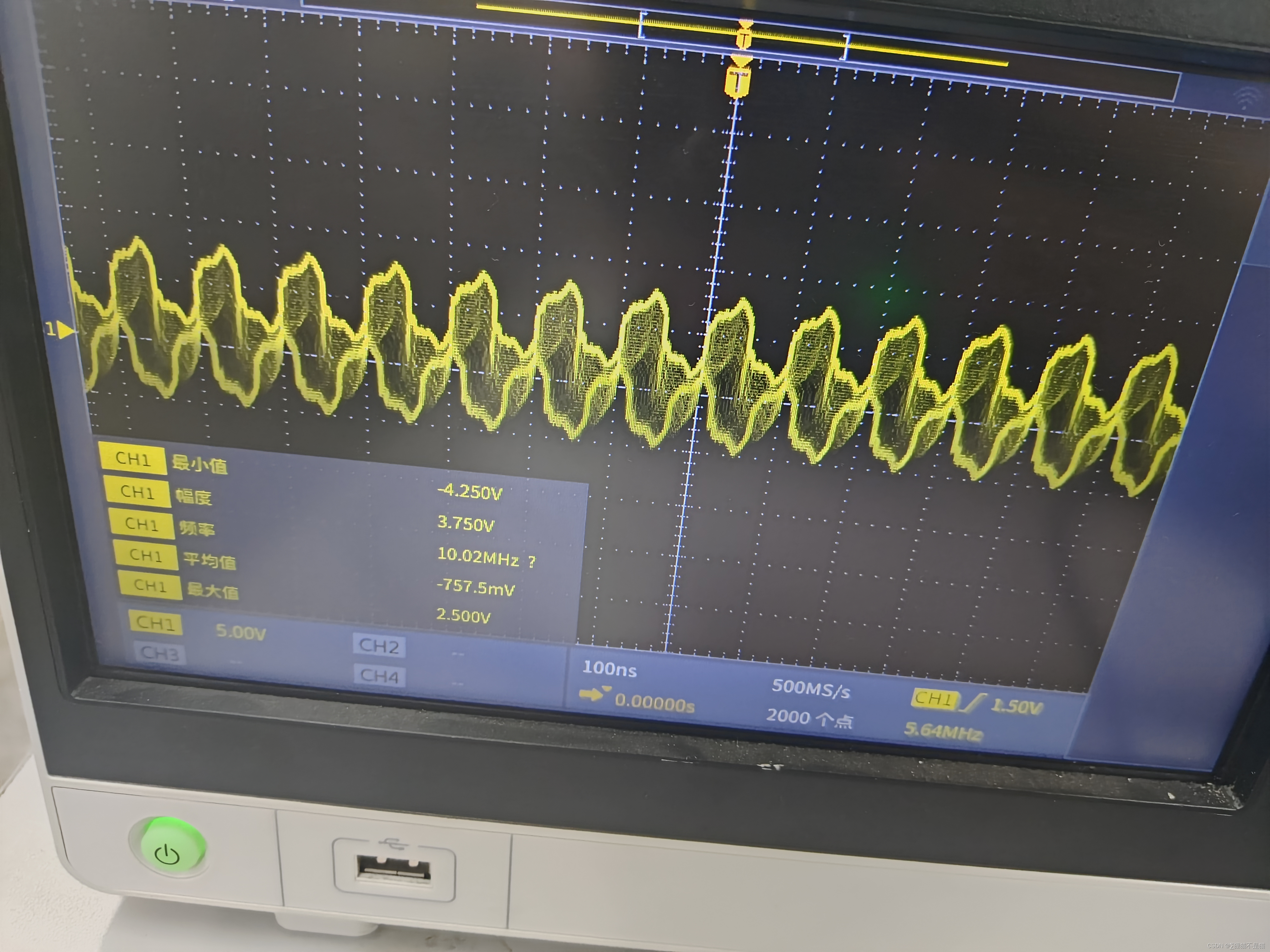

(7)实验现象:

原文地址:https://blog.csdn.net/2301_80417284/article/details/140143827

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!