ZYNQ中 PL 使用 PS 端晶振实现流水灯

ZYNQ中 PL 使用 PS 端晶振实现流水灯

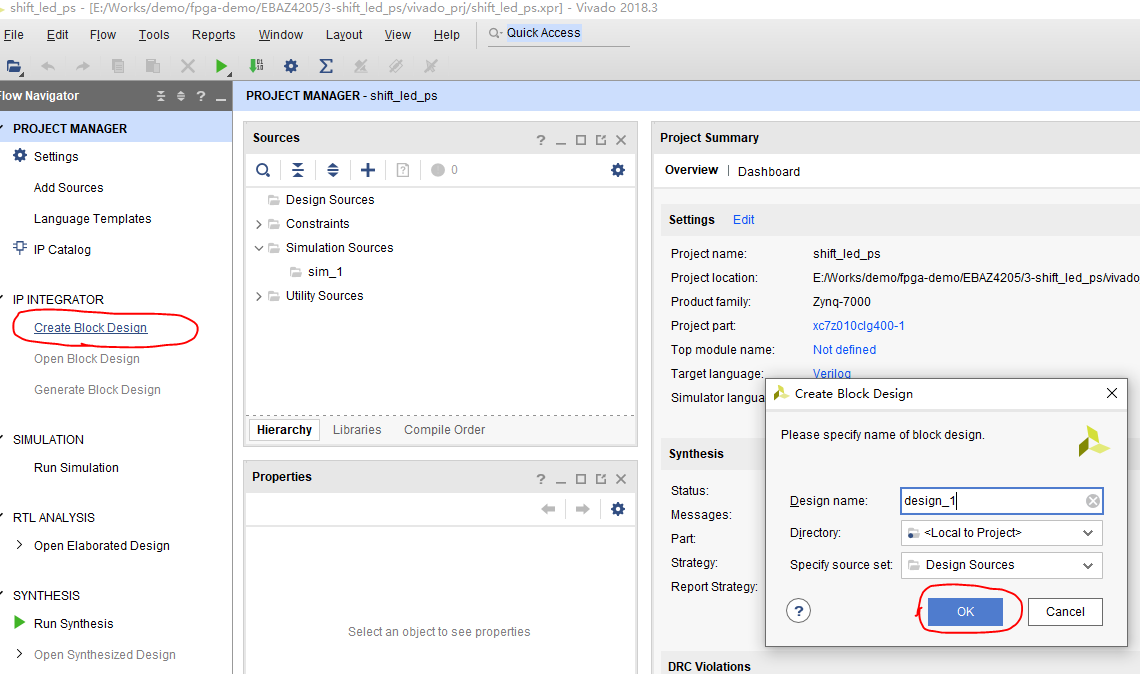

Create Block Design

点击 Create Block Design, 然后点击 OK:

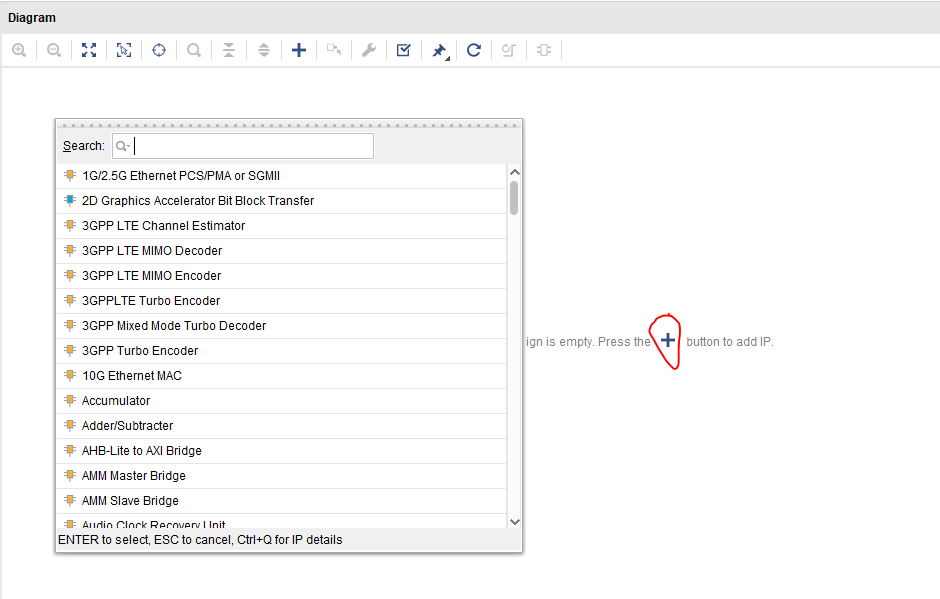

添加 IP 核

点击 Diagram 中的 + 号:

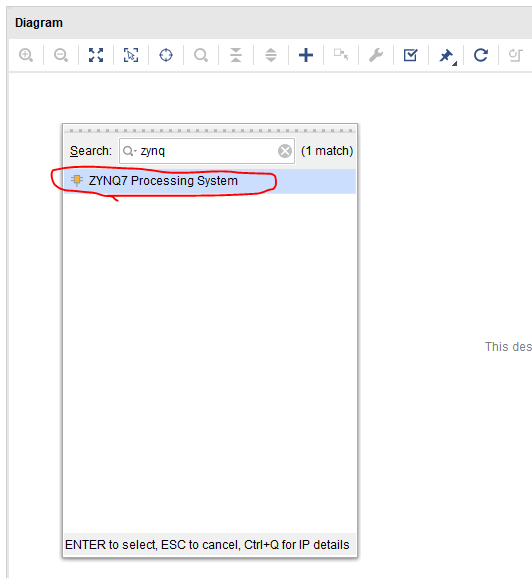

在 IP 核的搜索框中输入 ZYNQ, 找到 ZYNQ7 Processing System 的 IP 核,双击之:

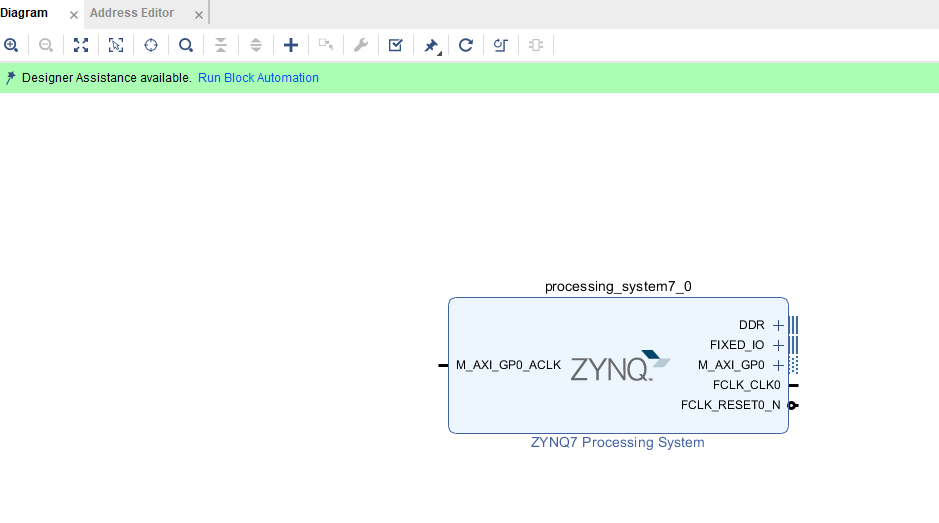

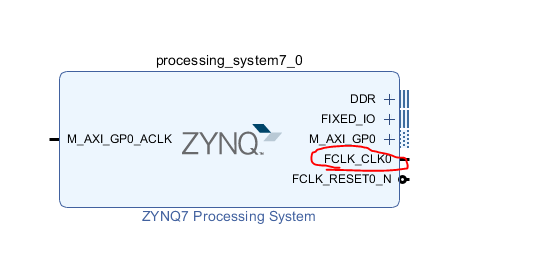

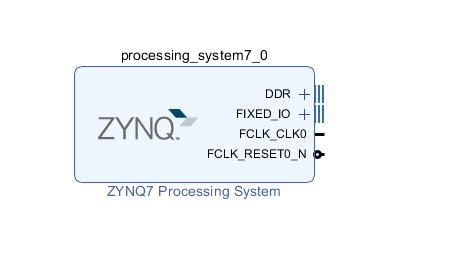

Viavado 会把 ZYNQ 的 IP 加到我们的 Block Design 中:

其中的 FCLK_CLK0 是默认的 PS 给到 PL 的时钟

基本配置

打开配置界面

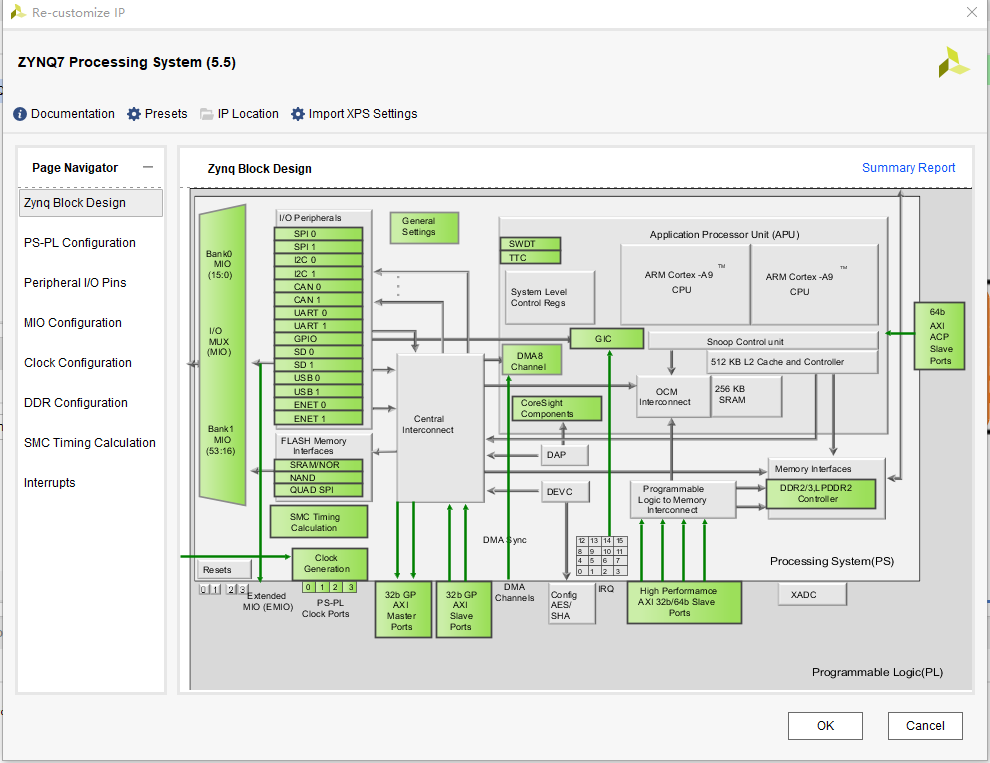

在 ZYNQ 上双击会弹出配置界面

上图中 MIO 的序号是 [15:0] [53:16], 也就是一共有 54 个 IO。

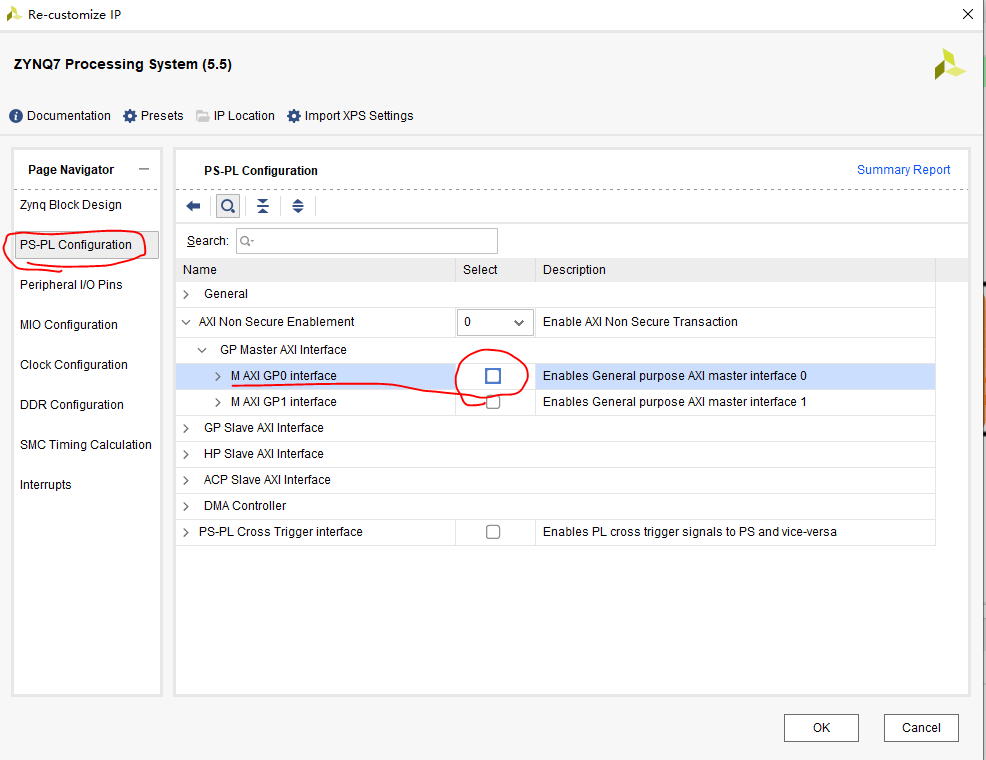

删除AXI 端口

AXI 端口暂时用不到, 去掉勾选,删除之:

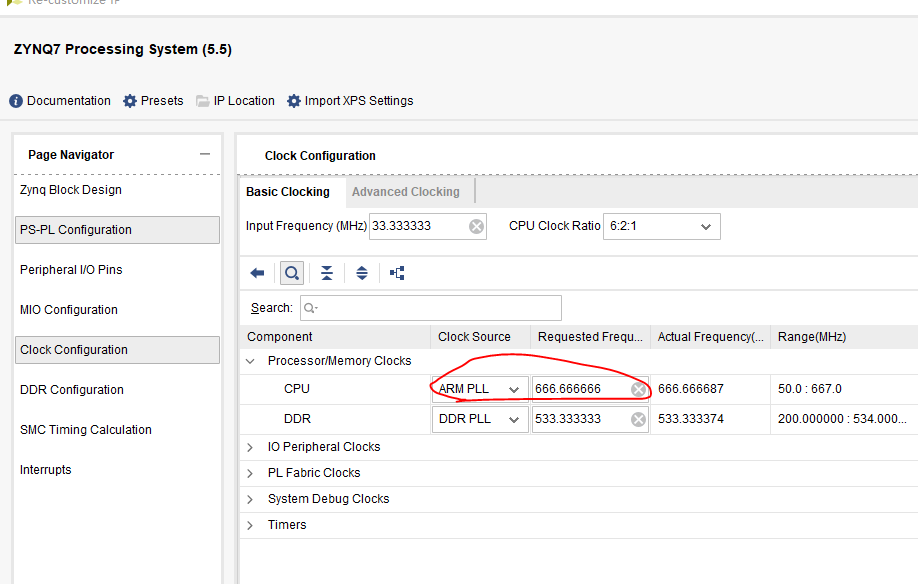

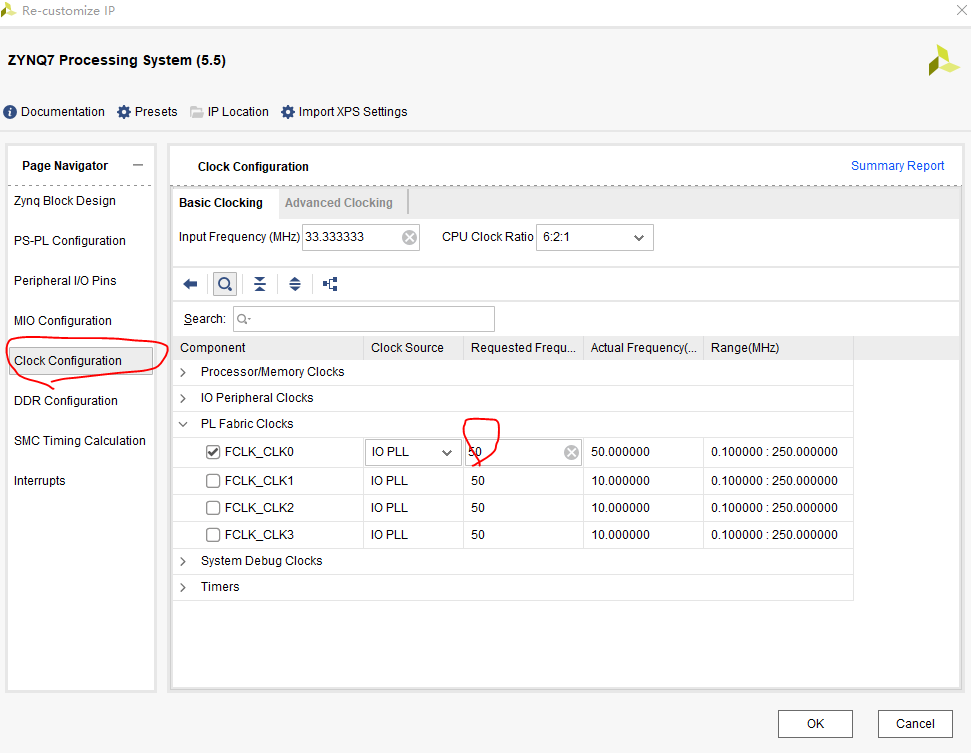

查看默认的输出时钟

可以看到默认是50M, 我们就不改了.

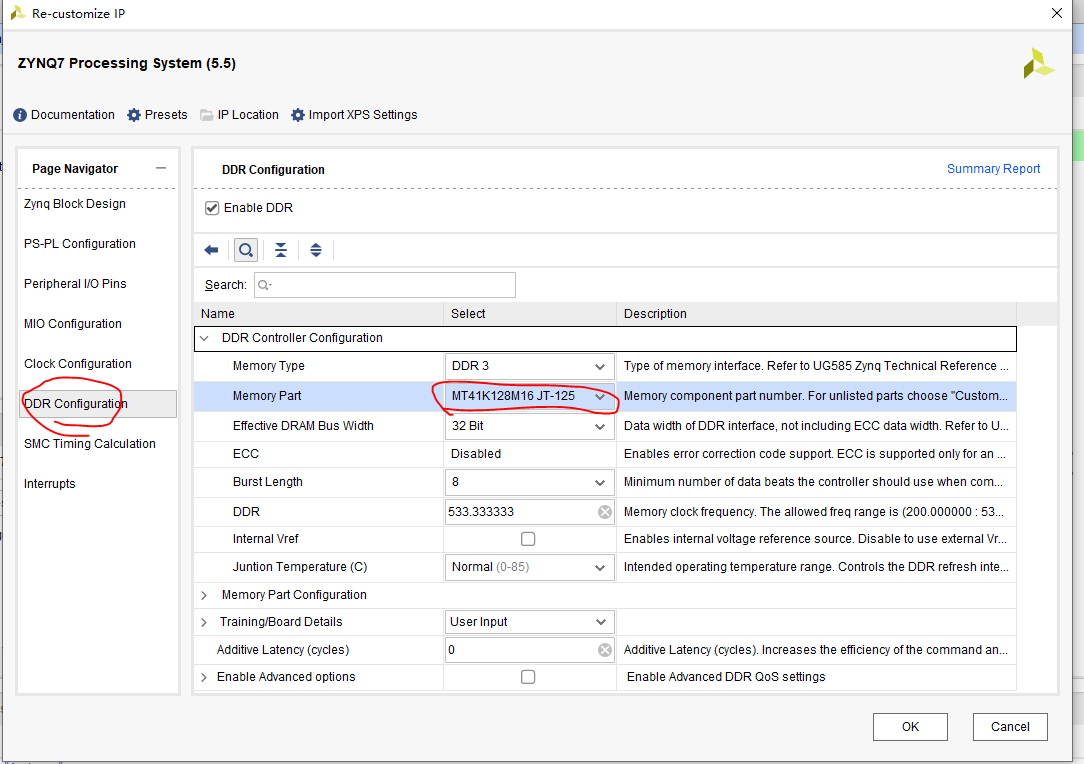

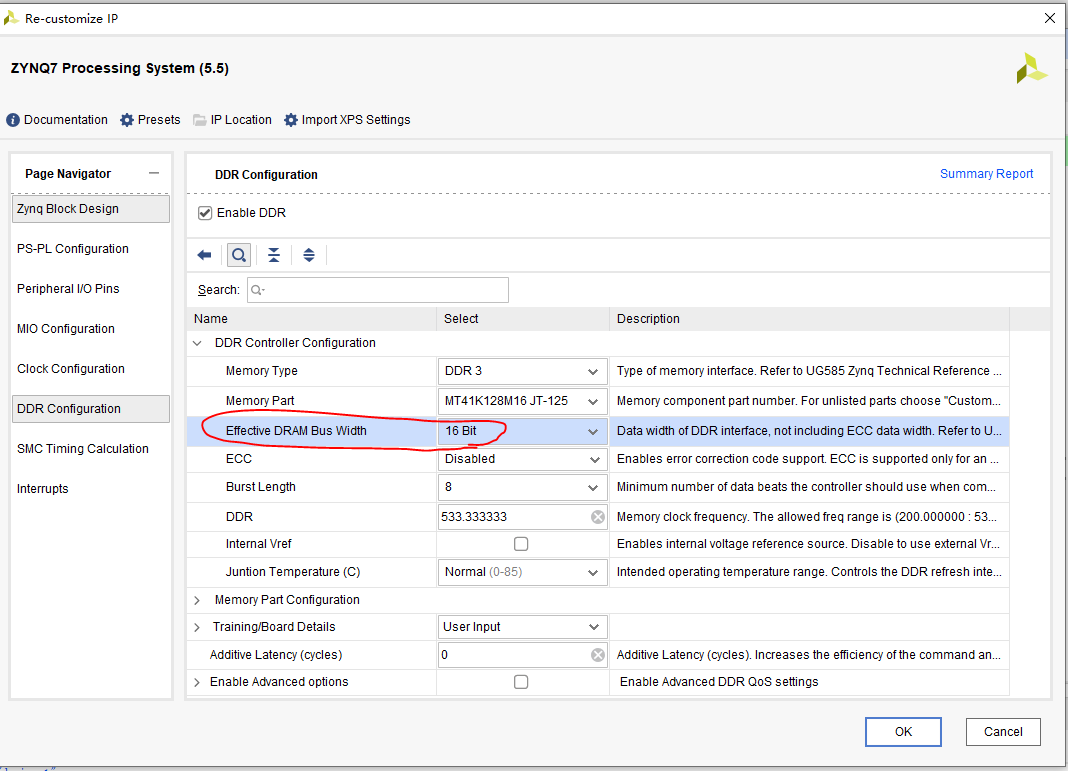

配置 DDR 3

1 设置 DDR3 的型号

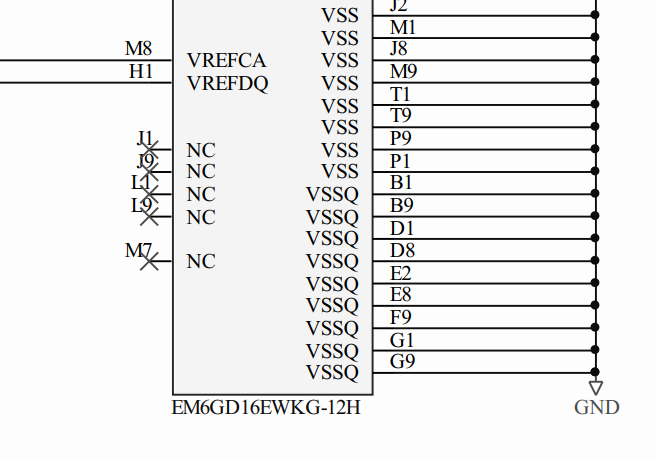

原理图中查看 DDR3 型号:

型号是: EM6GD16EWKG-12H.

Vivado 中没有上述型号,我们使用兼容型号: MT41K128M16 JT-125:

存储容量:128M*16=2048M bit = 2Gbit = 256M byte

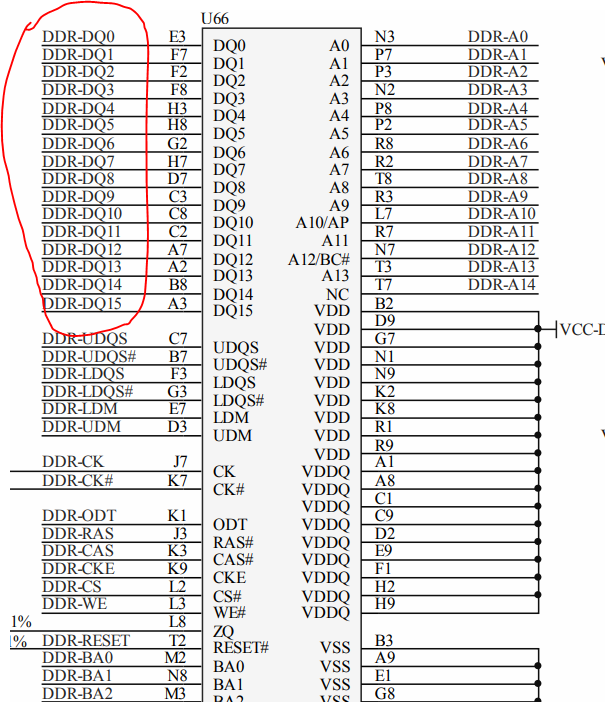

位宽:16 Bit :

其余的采用默认设置即可.

点击 OK,可以看到 原先 AXI 的端口已经没有了:

ZYNQ 使用 verilog 模块

两种方式:

-

把自己的模块打包成 IP 核

-

把自己的模块转换成 Block Design中的模块

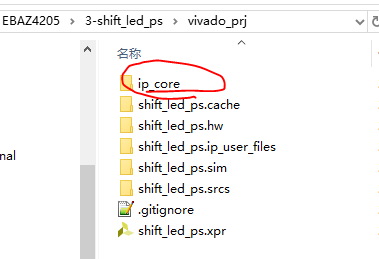

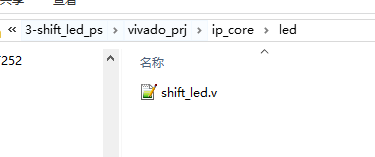

打包 IP 核

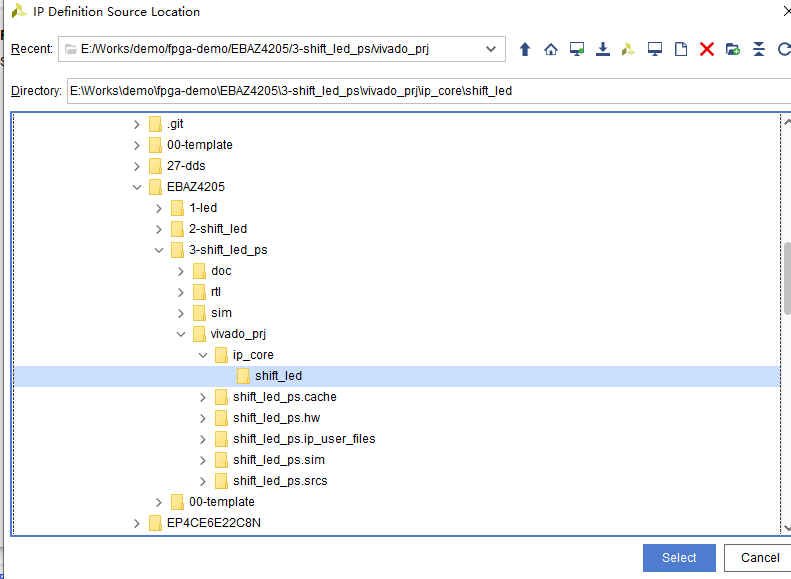

把模块复制到 工程中:

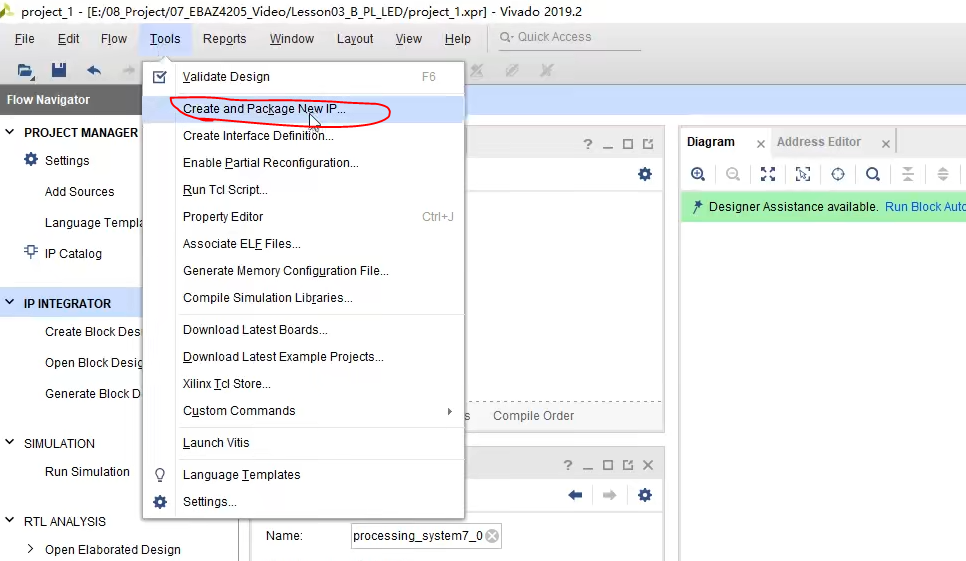

打开创建 IP 核窗口:

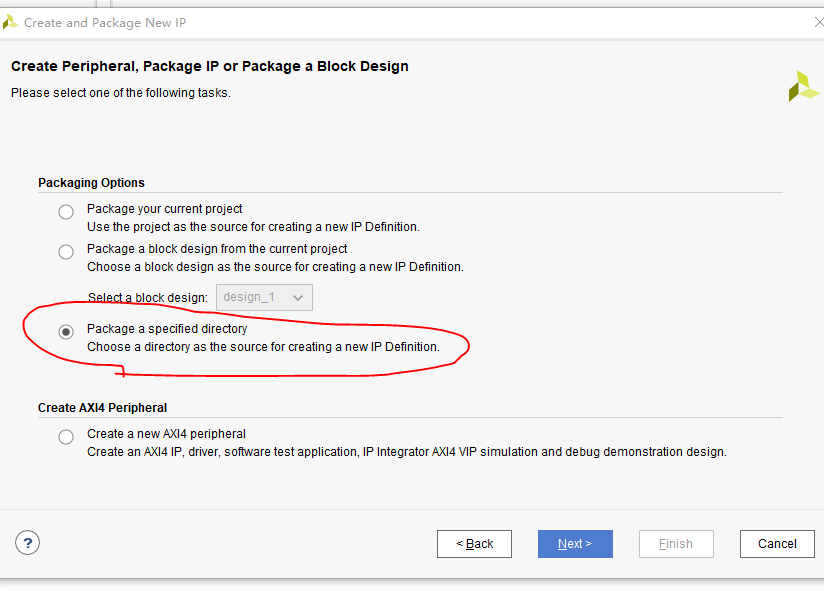

选择特定文件夹:

然后一路 Next 就可以了。

原文地址:https://blog.csdn.net/feiduoxuetang/article/details/142629186

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!