FPGA-学会使用vivado中的存储器资源ROM(IP核)

问题:

某芯片,有500个寄存器,需要在上电的时候由FPGA向这些寄存器中写入初始值,初始值已经通过相应的文档给出了具体值,这些值都是已知的。

分析关键点:

数据量比较多(Verilog代码,通过case语句、always语句这种查找表的方式,数据量比较大,很不方便)

数值都是已知的 (数据内容固定)

整个过程只需要工作一次

、

、

ROM : 只读存储器-----read only memory

非易失性,断电后数据不会丢失。嵌入电脑主板或者做移动存储介质就很合适,体积够小,提供的容量可以比光盘和软盘的大,速度也不慢。

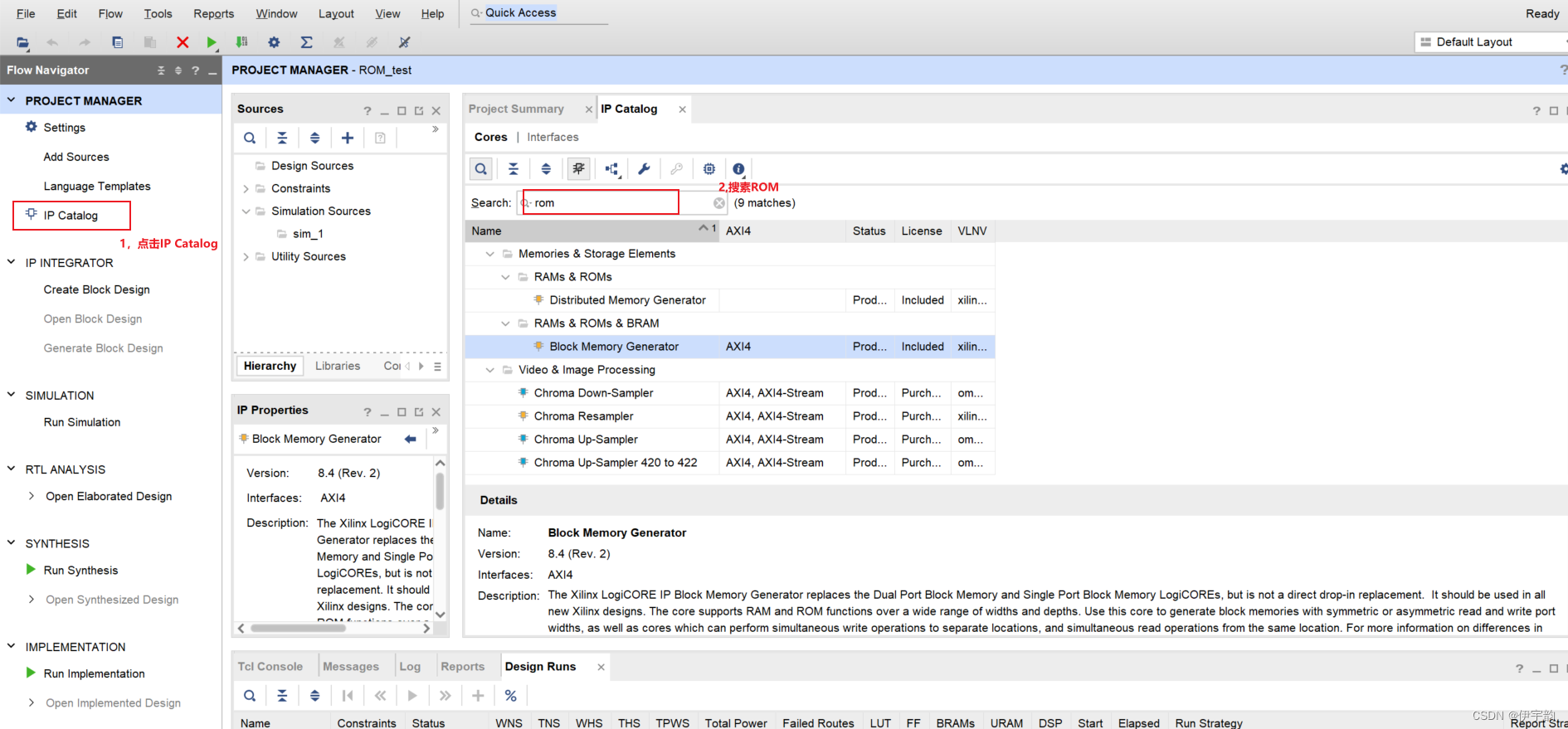

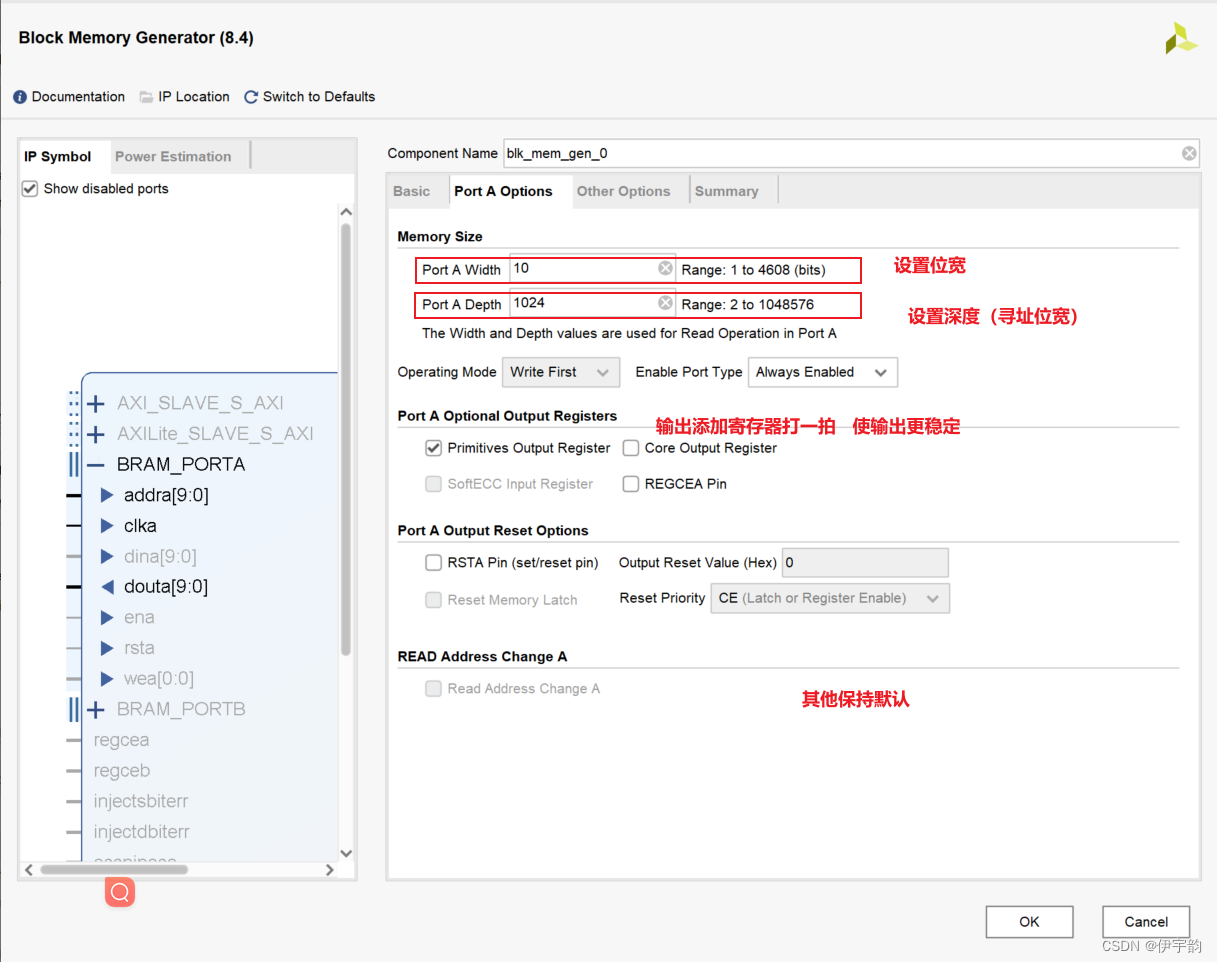

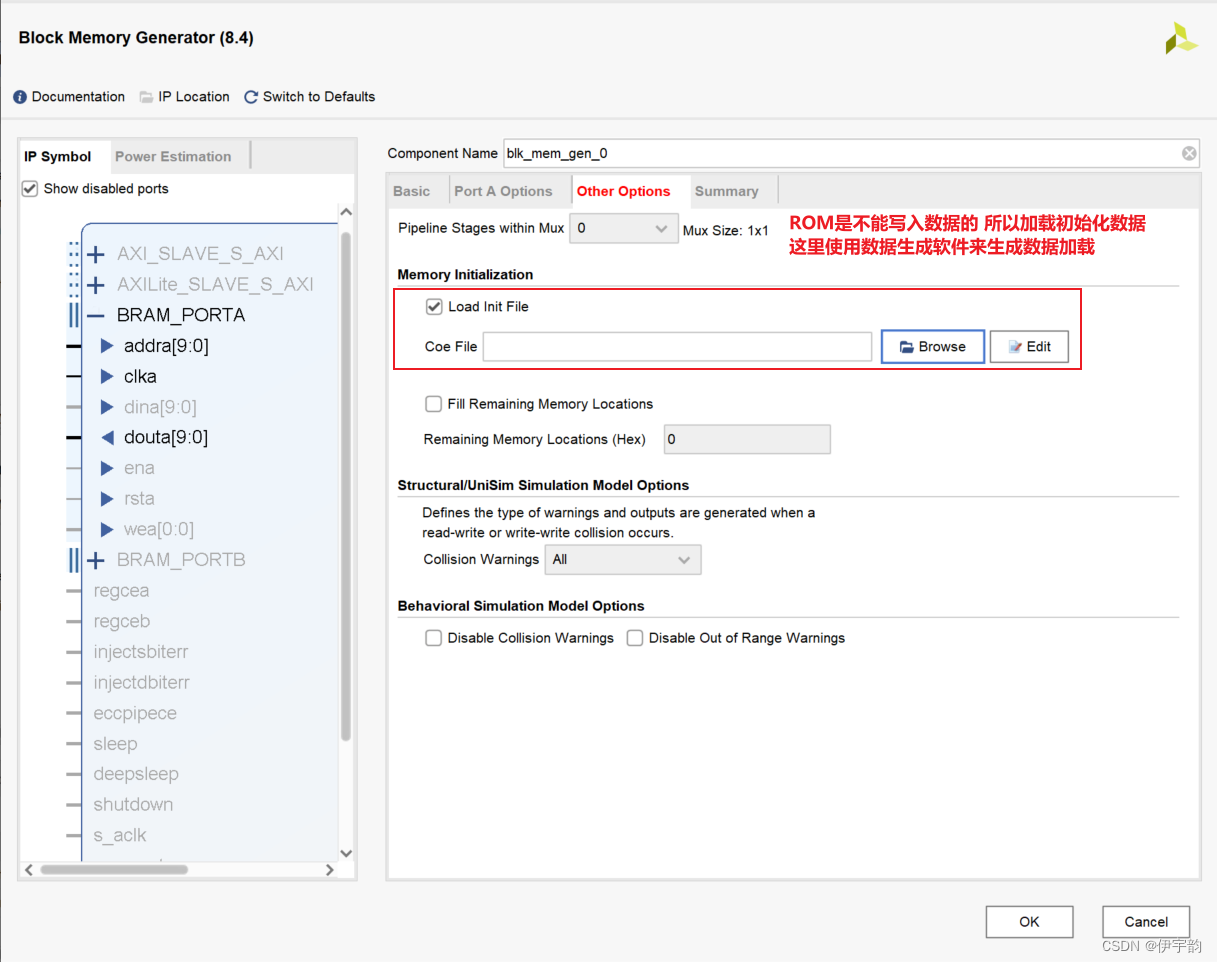

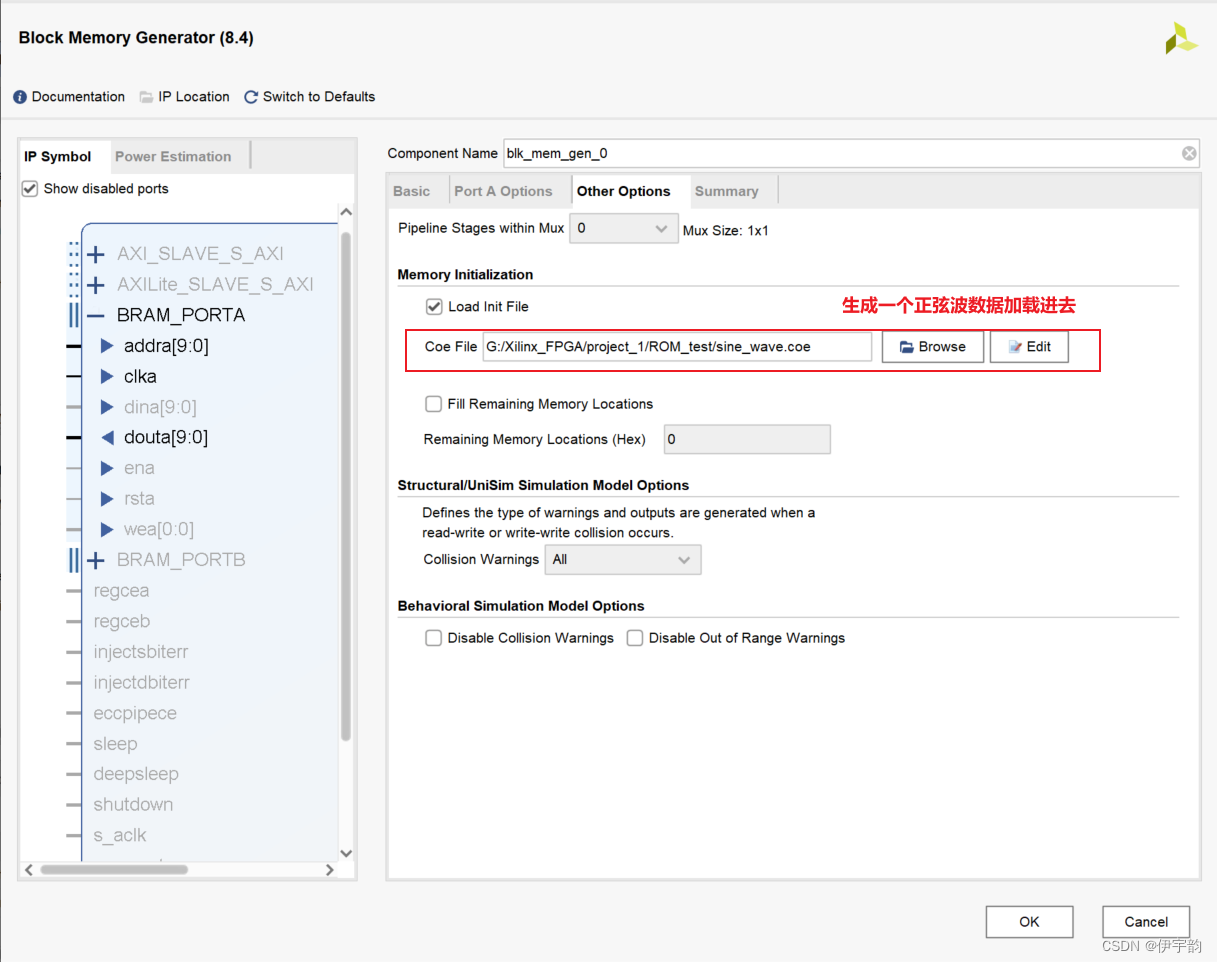

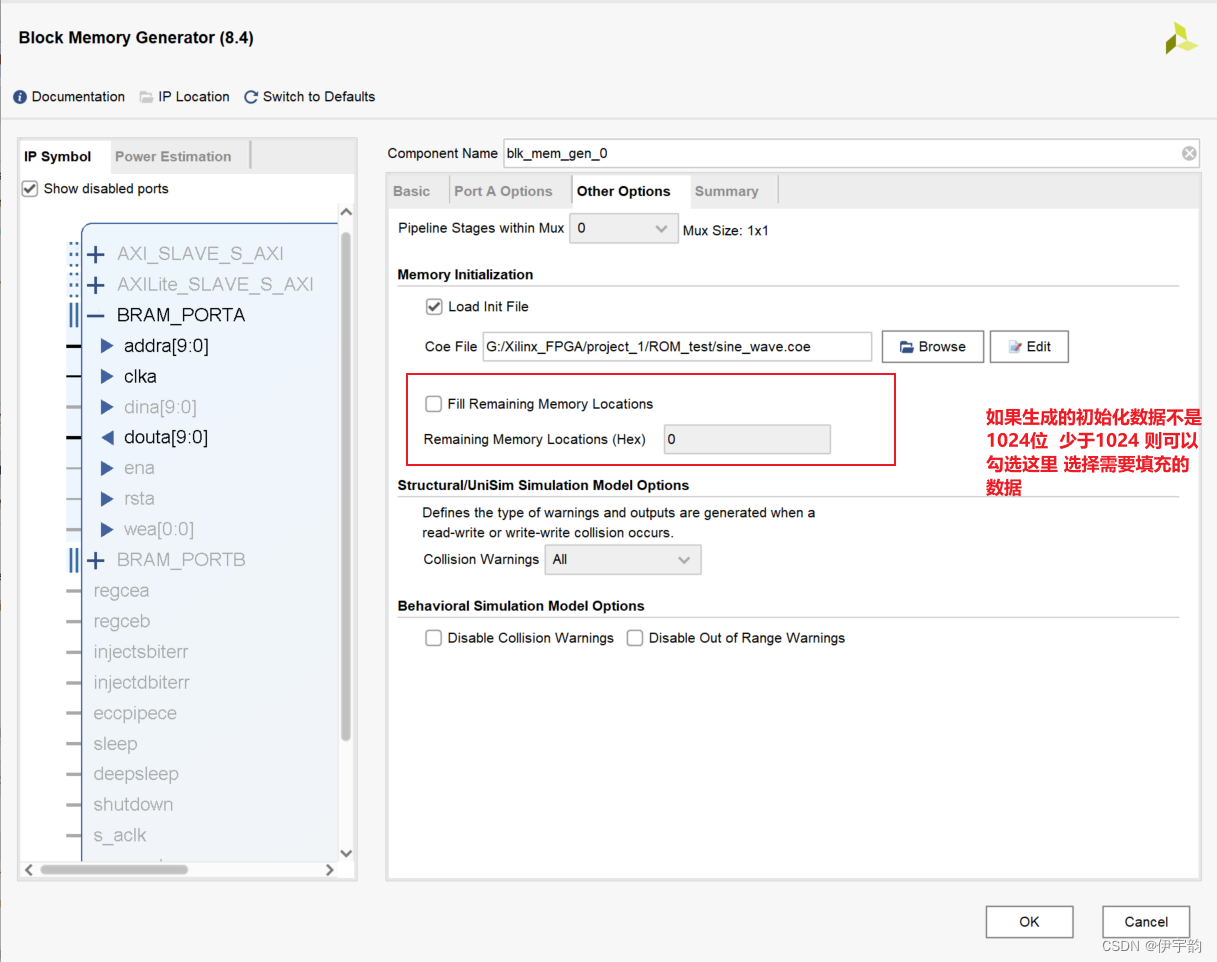

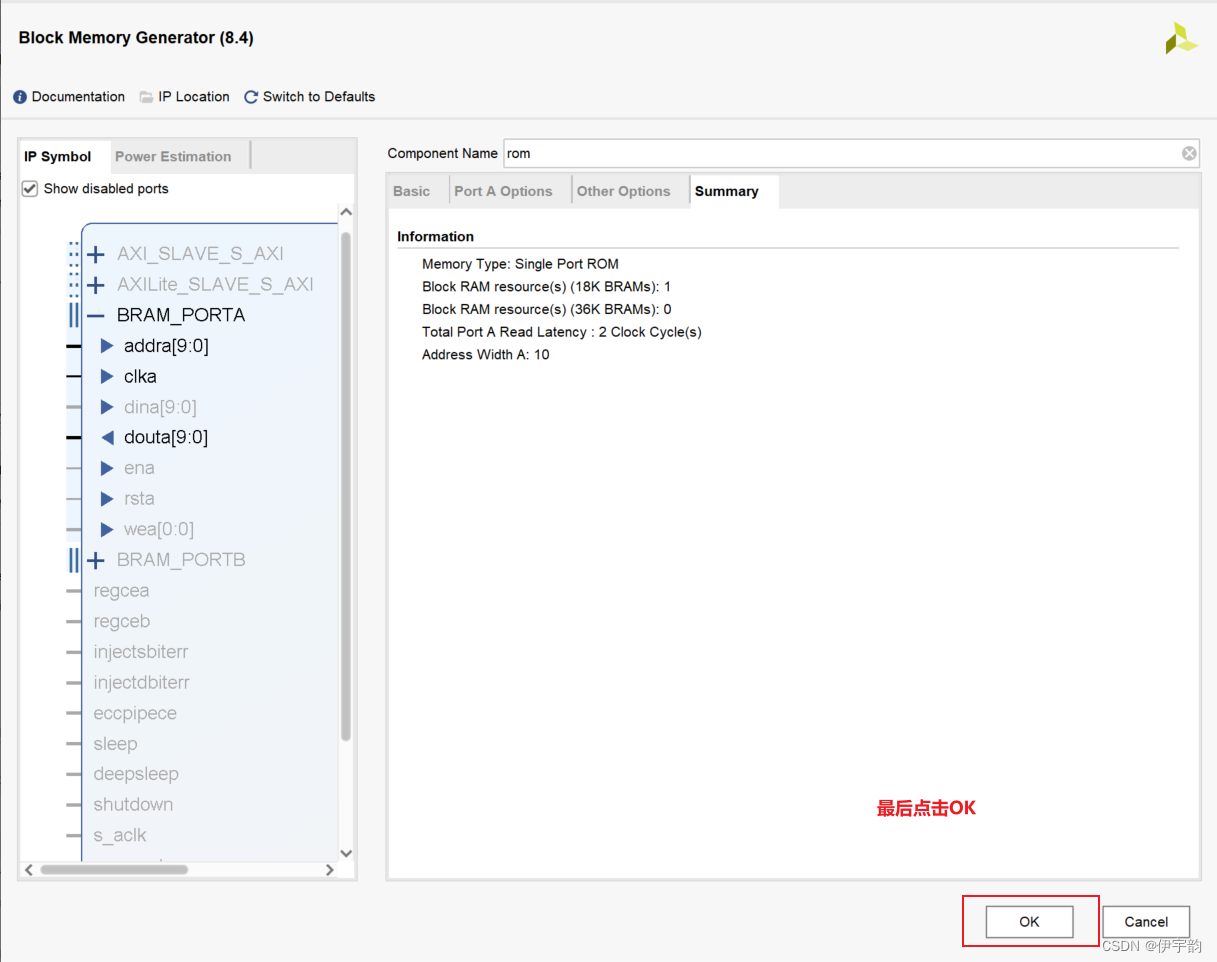

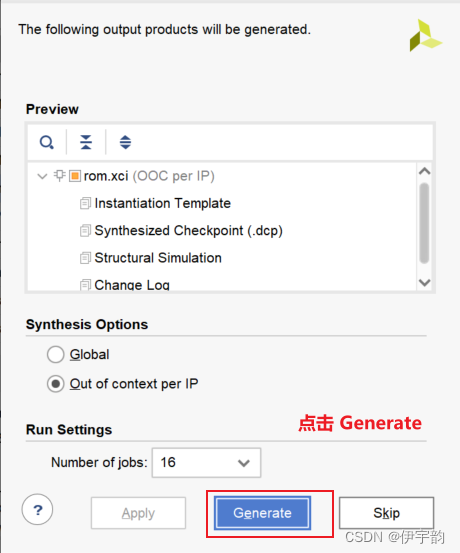

接下来 我们在Vivado中如何实现ROM IP核。

创建工程,进入Vivado界面

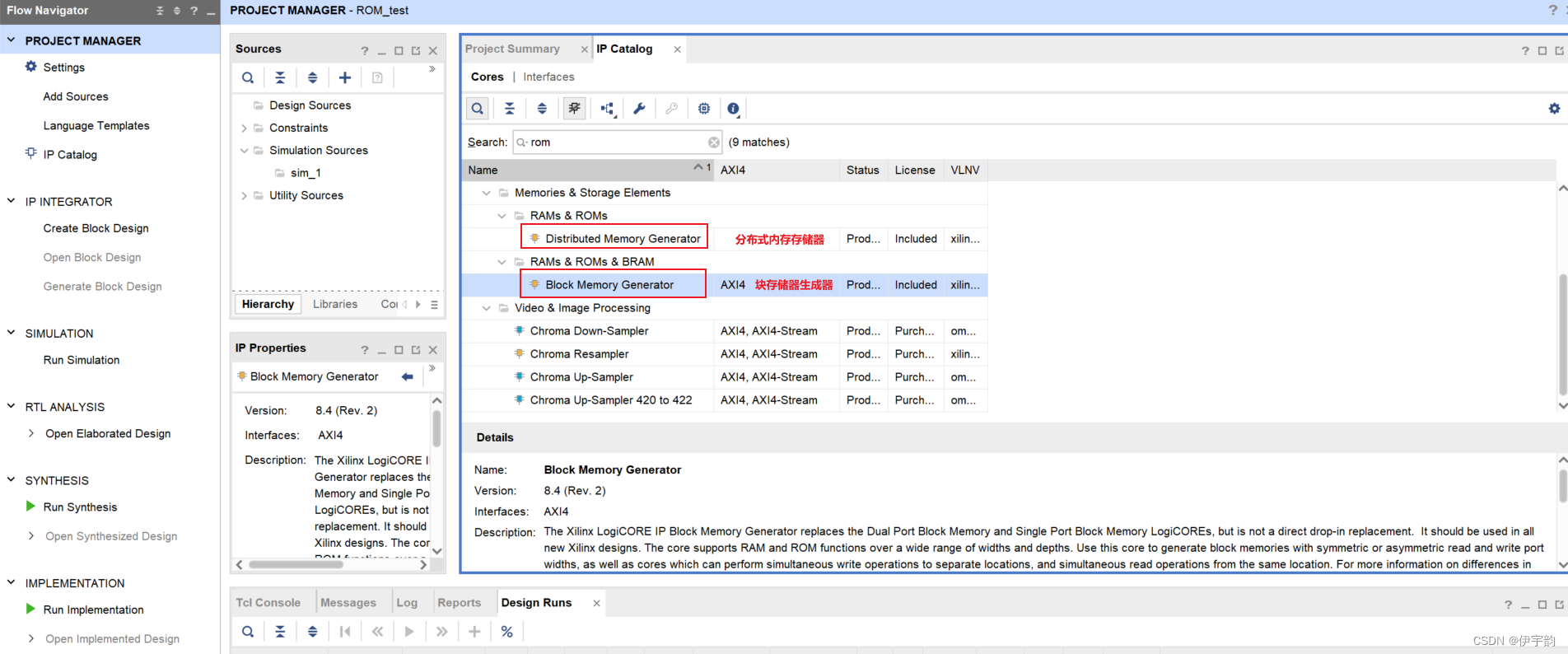

两者最主要的差别是生成的IP核所占用的FPGA资源不一样,

从Distributed Memory Generator 生成的ROM/RAM Core占用的资源是LUT (查找表,查找表本质就是一个小的RAM);

从Block Memory Generator生成的ROM/RAMCore 占用的资源是 Block Memory (嵌入式的硬件RAM) ,

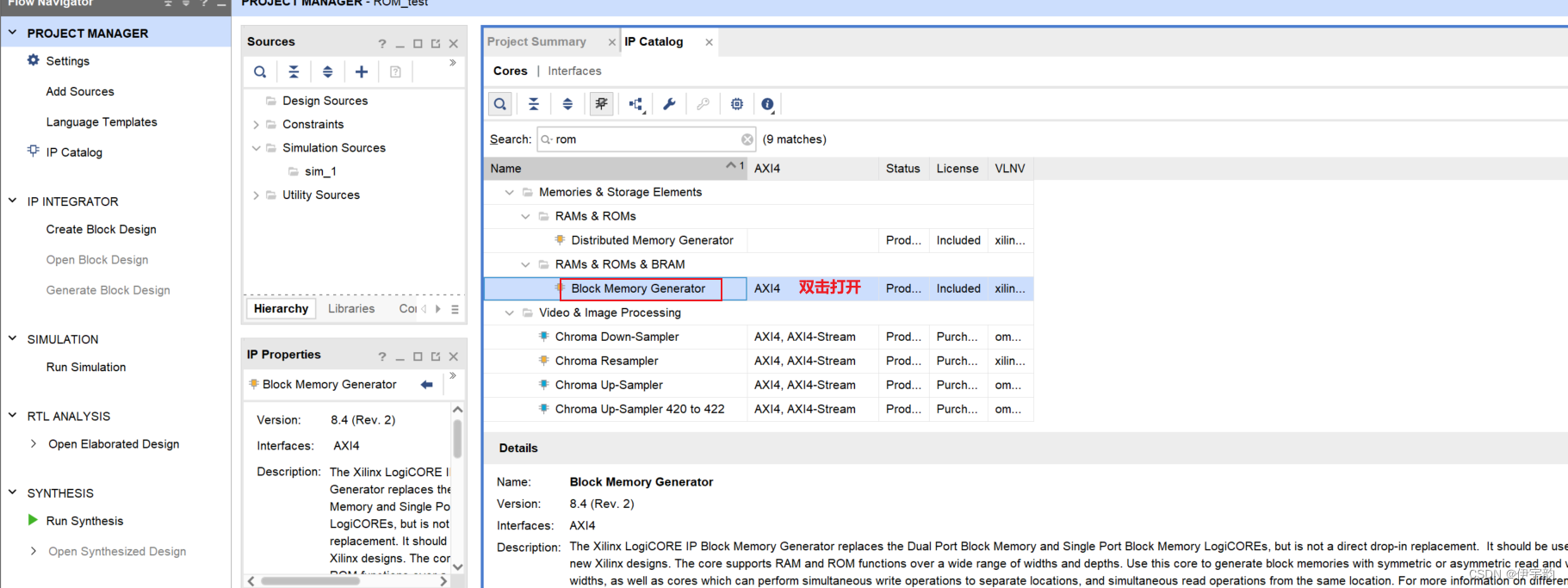

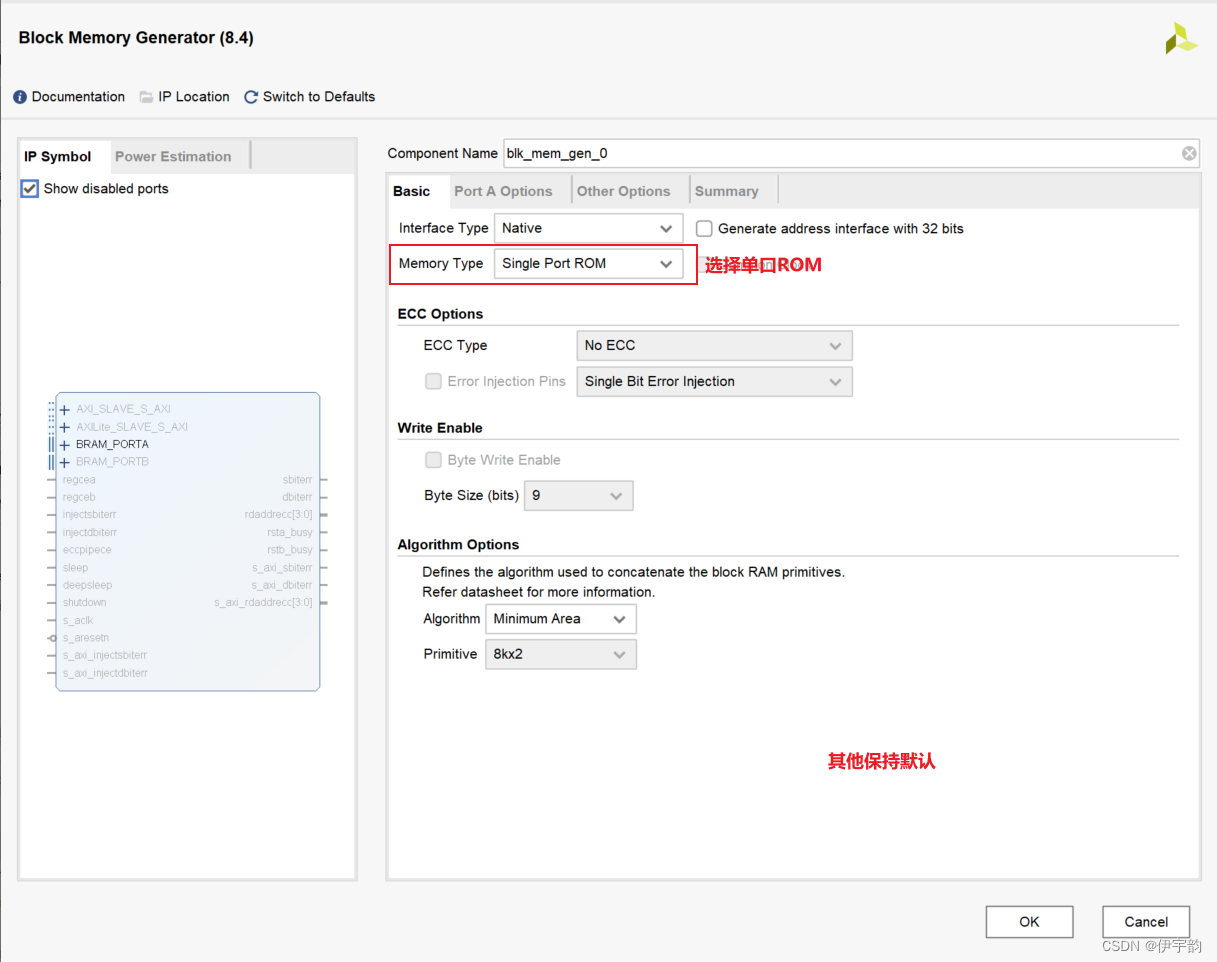

根据需求选择Block Memory Generator

然后编写ROM测试文件

代码如下

`timescale 1ns / 1ps

module rom_tb;

reg clka;

reg [9:0]addra;

wire [9:0]douta;

rom rom(

.clka(clka),

.addra(addra),

.douta(douta)

);

initial clka = 10;

always #10 clka = ~clka;

initial begin

addra = 100;

#201;

repeat(3000) begin

addra = addra + 1'd1;

#20;

end

#2000

$stop;

end

endmodule

仿真波形

然后把波形调为模拟输出

观察输出波形(正弦波)

原文地址:https://blog.csdn.net/weixin_46897065/article/details/136316635

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!