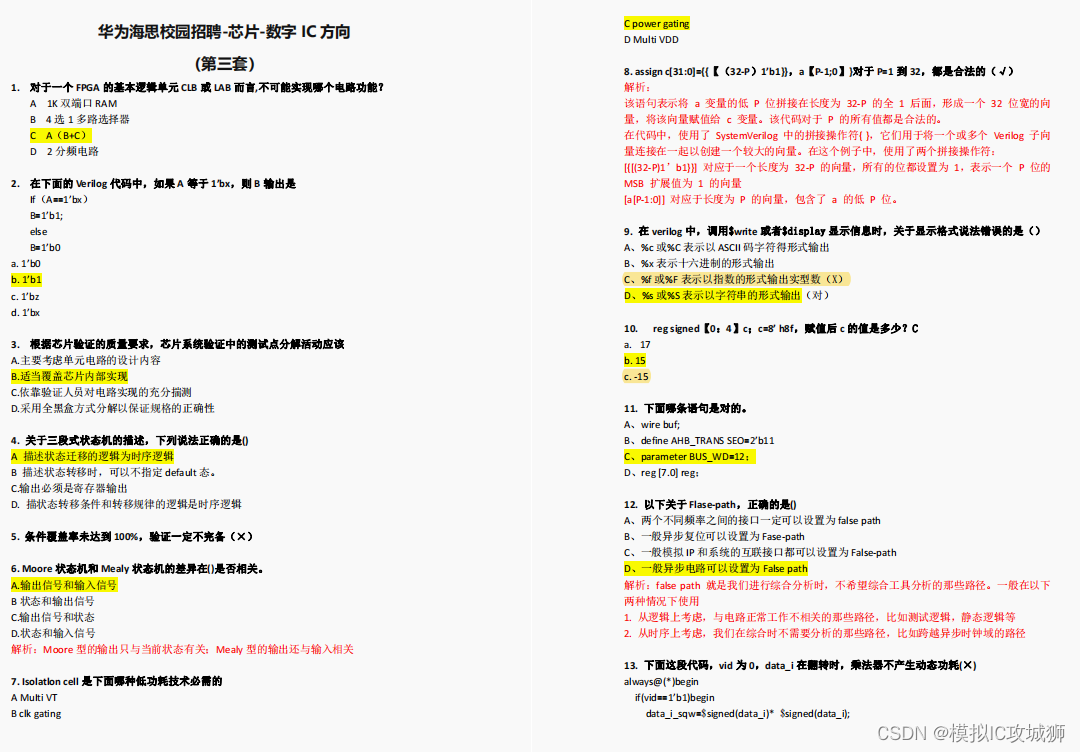

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第三套

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第三套

(共9套,有答案和解析,答案非官方,未仔细校正,仅供参考)

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

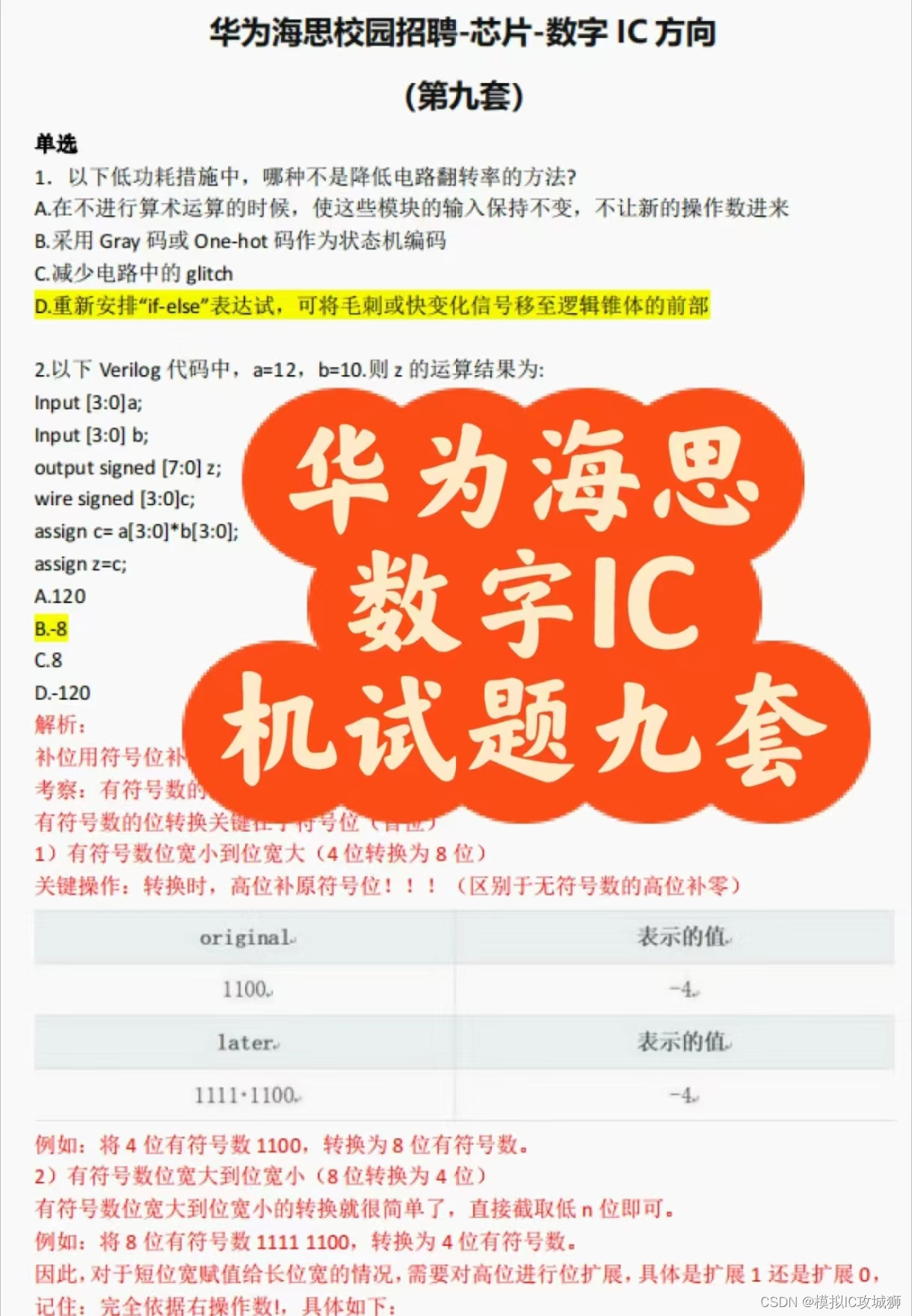

华为海思校园招聘-芯片-数字 IC 方向

(第三套)

- 对于一个 FPGA 的基本逻辑单元 CLB 或 LAB 而言,不可能实现哪个电路功能?

A 1K 双端口 RAM

B 4 选 1 多路选择器

C A(B+C)

D 2 分频电路 - 在下面的 Verilog 代码中,如果 A 等于 1’bx,则 B 输出是

If(A==1’bx)

B=1’b1;

else

B=1’b0

a. 1’b0

b. 1’b1

c. 1’bz

d. 1’bx - 根据芯片验证的质量要求,芯片系统验证中的测试点分解活动应该

A.主要考虑单元电路的设计内容

B.适当覆盖芯片内部实现

C.依靠验证人员对电路实现的充分揣测

D.采用全黑盒方式分解以保证规格的正确性

4. 关于三段式状态机的描述,下列说法正确的是()

A 描述状态迁移的逻辑为时序逻辑

B 描述状态转移时,可以不指定 default 态。

C.输出必须是寄存器输出

D. 描状态转移条件和转移规律的逻辑是时序逻辑

5. 条件覆盖率未达到 100%,验证一定不完备(×) - Moore 状态机和 Mealy 状态机的差异在()是否相关。

A.输出信号和输入信号

B 状态和输出信号

C.输出信号和状态

D.状态和输入信号

解析:Moore 型的输出只与当前状态有关;Mealy 型的输出还与输入相关 - Isolatlon cell 是下面哪种低功耗技术必需的

A MuIti VT

B clk gating

C power gating

D Multi VDD - assign c[31:0]={{【(32‐P)1’b1}},a【P‐1;0】}对于 P=1 到 32,都是合法的(√)

解析:

该语句表示将 a 变量的低 P 位拼接在长度为 32‐P 的全 1 后面,形成一个 32 位宽的向

量,将该向量赋值给 c 变量。该代码对于 P 的所有值都是合法的。

在代码中,使用了 SystemVerilog 中的拼接操作符{ },它们用于将一个或多个 Verilog 子向

量连接在一起以创建一个较大的向量。在这个例子中,使用了两个拼接操作符:

[{[(32‐P)1’b1}}] 对应于一个长度为 32‐P 的向量,所有的位都设置为 1,表示一个 P 位的

MSB 扩展值为 1 的向量

[a[P‐1:0]] 对应于长度为 P 的向量,包含了 a 的低 P 位。 - 在 verilog 中,调用

w

r

i

t

e

或者

write 或者

write或者display 显示信息时,关于显示格式说法错误的是()

A、%c 或%C 表示以 ASCII 码字符得形式输出

B、%x 表示十六进制的形式输出

C、%f 或%F 表示以指数的形式输出实型数(X)

D、%s 或%S 表示以字符串的形式输出(对) - reg signed【0:4】c;c=8’ h8f,赋值后 c 的值是多少?C

a. 17

b. 15

c. ‐15 - 下面哪条语句是对的。

A、wire buf;

B、define AHB_TRANS SEO=2’b11

C、parameter BUS_WD=12;

D、reg [7.0] reg; - 以下关于 Flase‐path,正确的是()

A、两个不同频率之间的接口一定可以设置为 false path

B、一般异步复位可以设置为 Fase‐path

C、一般模拟 IP 和系统的互联接口都可以设置为 False‐path

D、一般异步电路可以设置为 False path

解析:false path 就是我们进行综合分析时,不希望综合工具分析的那些路径。一般在以下

两种情况下使用 - 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态逻辑等

- 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径

- 下面这段代码,vid 为 0,data_i 在翻转时,乘法器不产生动态功耗(×)

always@()begin

if(vid==1’b1)begin

data_i_sqw=$signed(data_i) KaTeX parse error: Double subscript at position 45: …gin data_i_̲sqw=16’d0; end…unsigned(‐4)

A.8’b0000_0100

B.8’b1111_0011

C 8’b1111_1100

D.8’b0000_0011

解析:

对于 SystemVerilog 中的 unsigned 类型,其值域为 0 到 2^N‐1,其中 N 表示变量的位宽。

因此,unsigned(‐4) 的值为 2^8 ‐ 4 = 252。

用二进制表示 252,需要 8 位二进制数。其二进制表示为 1111 1100。因此,正确的答案是

D. 8’b0000_0011。

19. 在编写时序逻辑代码时,下列哪个方法不能明显降低动态功耗

A.将不必要的置 0/置 1 修改为保持

B 降低时钟频率

C.时钟门控

D. 使用不带复位的寄存器

20. Verilog 语言的层次从低到高依次对应()

A、门级,寄存器传输级,行为级,功能级,系统级

B、系统级,功能级,寄存器传输级,行为级,门级,行为级,寄存器传输级,功能级,系

统级

C、门级,寄存器传输级,功能级,行为级,系统级

D、门级,功能级,寄存器传输级,行为级,系统级

21. 状态机的基本要素中包括:状态、输入,输出和健壮性(×)

解析:输入、输出、状态

22. reg[255:0] mem[15:0];该声明定义了一个位宽为 16Bits,深度为 256 的 Memory(×)

解析:该声明定义了一个位宽为 256bits,深度为 32 的 memory。

23. SystemVerilog 随机只支持两态值,四态值(X 或 Z)或四态操作符(如==,!==)在随机中使

用是非法的并且会导致错误(√)

24. SystemVerilog Asserion 中,express1|=>express2,表示如果 express1 为真,则在当前时刻检

查 express2,如果 express2 为真则断开。(×)

25. 以下语句,哪个不可综合?

A、generate 语

B、wait 语句

C、if 语句

D、for 语句

解析:

可综合语句:

input、output、parameter、reg、wire、always、assign、begin、end、case、 posedge、negedge、

or、and、default、if、function、generate、integer、`define, while、repeat、for(while、repeat

循环可综合时,要具有明确的循环表达式和循环条件,for 可综合时也要有具体的循环范围)

不可综合语句:

initial、fork…join、wait、time、real、display、 forever.

26. 高频时钟域的总线数据(可能每个时钟周期数据都发生变化)传递给低频时钟域时,哪种

同步方式正确()

原文地址:https://blog.csdn.net/wang201938/article/details/137682480

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!