DDS笔记

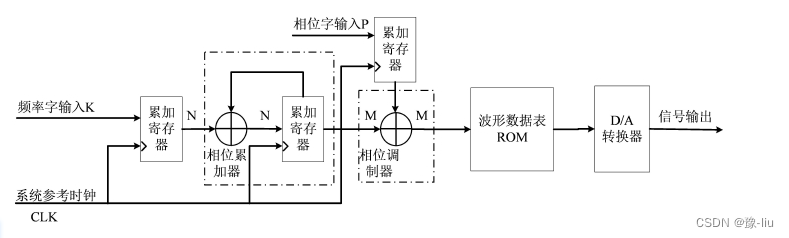

1.DDS 直接数字式频率合成器(Direct Digital Synthesizer,DDS)是通过相位和幅值

的映射实现任意频率的正弦曲线样本的方法

系统时钟CLK频率为fclk,输出信号频率为fout,频率字输入K的位宽为N位。

相位累加器通常由一个N位加法器和一个N位寄存器组成。在采样时钟的每个周期频率字输入K进入加法器与寄存器内存储的结果进行相加,累加的结果更新到寄存器,等待下一个采样时钟周期继续作为加法器的输入与FTW进行 累加。当累加的结果超过N位寄存器的所表示的最大值,溢出的高位将会被舍 弃,按照低N位结果输出到下一级。

在平均/K个参考时钟周期内,相位累加器会发生一次 溢出,即在一个正弦波周期,系统时钟次数是

/K,该发生溢出的时间即为DDS生成信号周期,那么DDS生成周期可表示为

Tout = (/K)*(1/fclk)

DDS生成频率可表示为

fout=K*fclk/

N为寄存器的位宽,即一个正弦波周期寄存器存的相位为,所以最小相位分辨率为2Π/

;

从相位角度来说,频率字输入K相当于相位增量,在固定系统参考时钟的情 况下,相位增量越小,周期时间越长,输出的信号频率越小。因此当K取1时,输出信号的最小频率为:

foutmin=fclk/

输出信号的最小频率也可以称为频率分辨率,固定系统时钟频率时,频率字输入K的位宽N越大,频率分辨率也就越小。

根据奈奎斯特采样定律,当输出信号频率fout大于或等于fcclk/2时,容易引起fout 与杂散靠得很近,导致最终杂散难以滤除。一般将DDS输出的最高频率设定为系统参考时钟的0.4倍,避免输出频谱的混叠。因此,最终产生的信号需要一个具有陡峭截止响应的低通滤波器来有效降低带外频率分量的幅度。

原文地址:https://blog.csdn.net/fengzhiwu3/article/details/136387663

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!