LPDDR4芯片学习(四)——DDR Training

一、ZQ Calibration

DDR 学习时间 (Part B - 6):DRAM ZQ 校正 - 知乎 (zhihu.com)

从原理上解释什么是DDR的ZQ校准? - 知乎 (zhihu.com)

LPDDR4的训练(training)和校准(calibration)--ZQ校准(Calibration)_wonder_coole-腾讯云开发者社区

01 ZQ校准的目的

为了提高信号完整性,并增强输出信号的强度,DDR内存中引入了终端电阻和输出驱动器,而为了在温度和电压发生变化的场景下仍然能够保持信号完整性,就需要对这些终端电阻和输出驱动器进行校准;

未经校准的终端电阻会直接影响到信号质量,而调整不当的输出驱动器则会使得有效信号跃迁偏离参考电平,从而导致数据和选通信号之间出现偏差。

【DRAM存储器二十二】DDR3介绍-主要功能之ZQ校准_ddr zq校准-CSDN博客

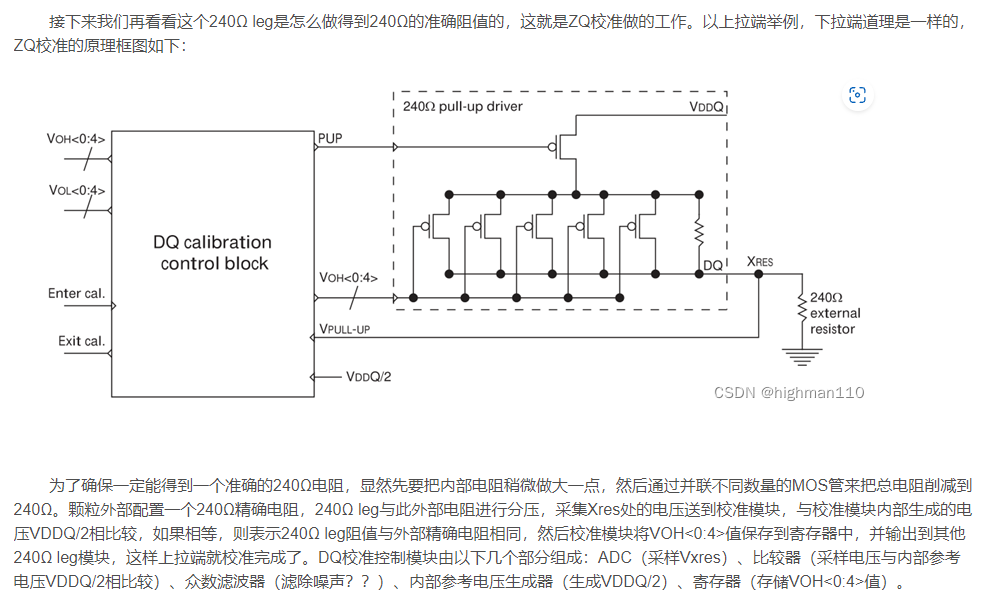

02 ZQ校准原理

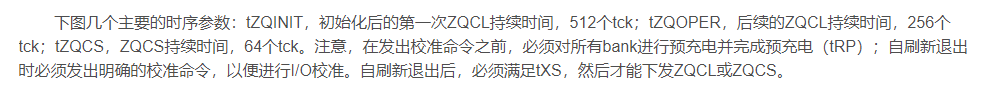

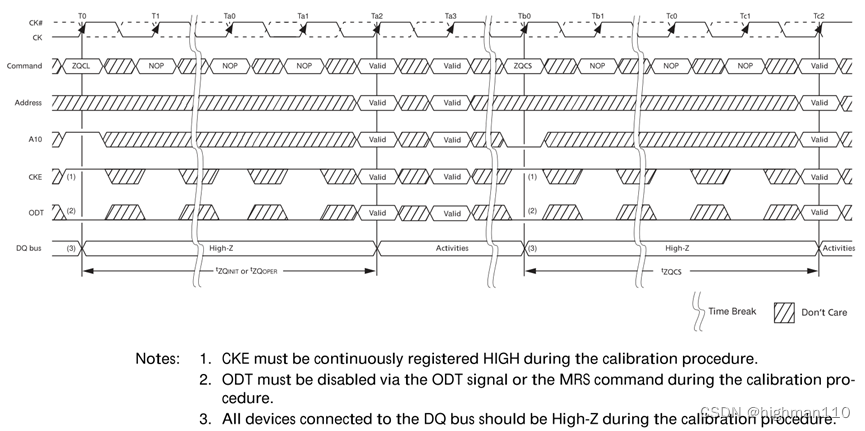

03 ZQ校准时序

二、VREF Training

【DRAM存储器三十五】LPDDR4介绍--主要技术特性之VREF training,为什么要做VREF training?-CSDN博客

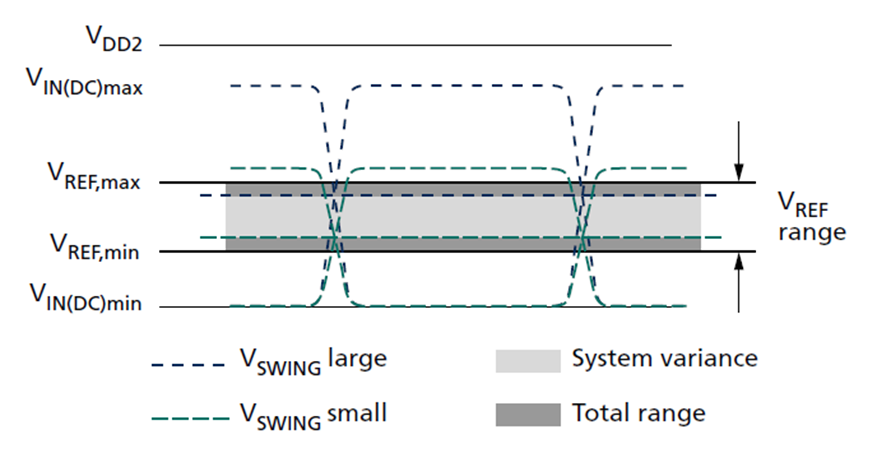

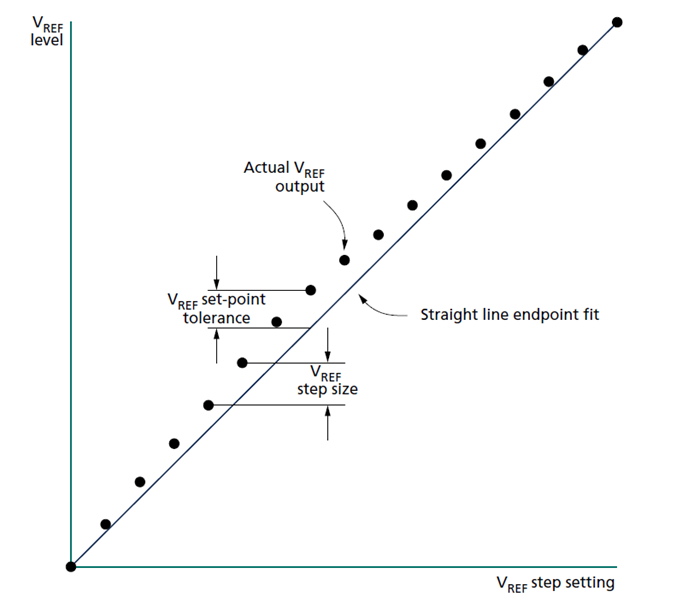

01 VREF DQ Training

-

Vref DQ Training 在DQ Training完成

-

MR14 OP[5:0] : VREF(DQ) Setting

02 VREF CA Training

-

Vref CA Training 在Command Bus Training完成

-

MR14 OP[6] : VREF(DQ) Range

三、CA Training

LPDDR4学习笔记(八)之command bus training-CSDN博客

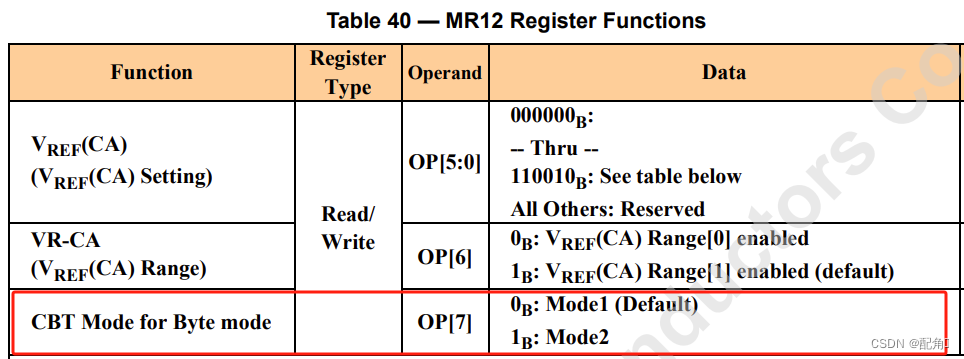

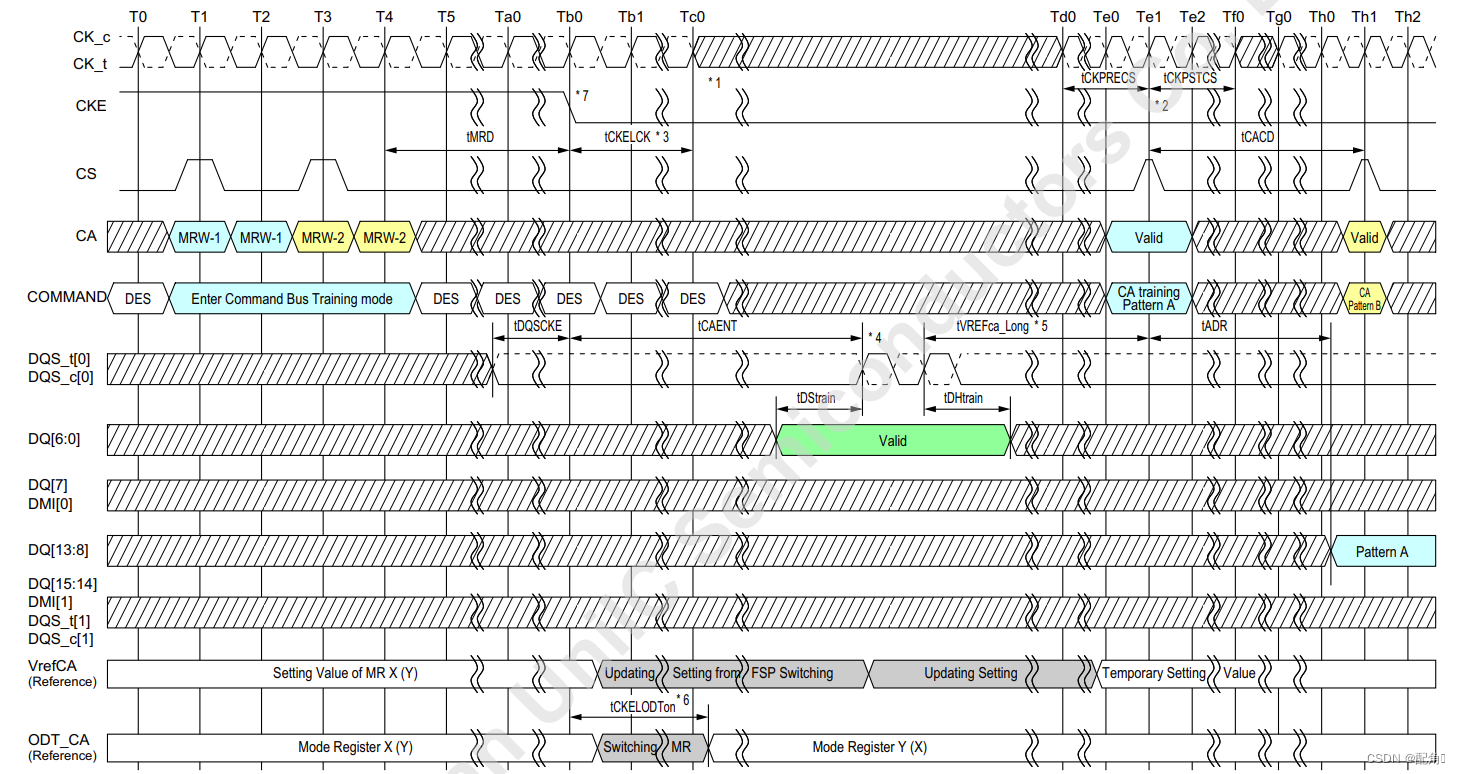

01 Command Bus Training

CBT: Command Bus Training

-

在高频操作之前Training

-

两种Training模式,由MR12 OP[7]来进行配置

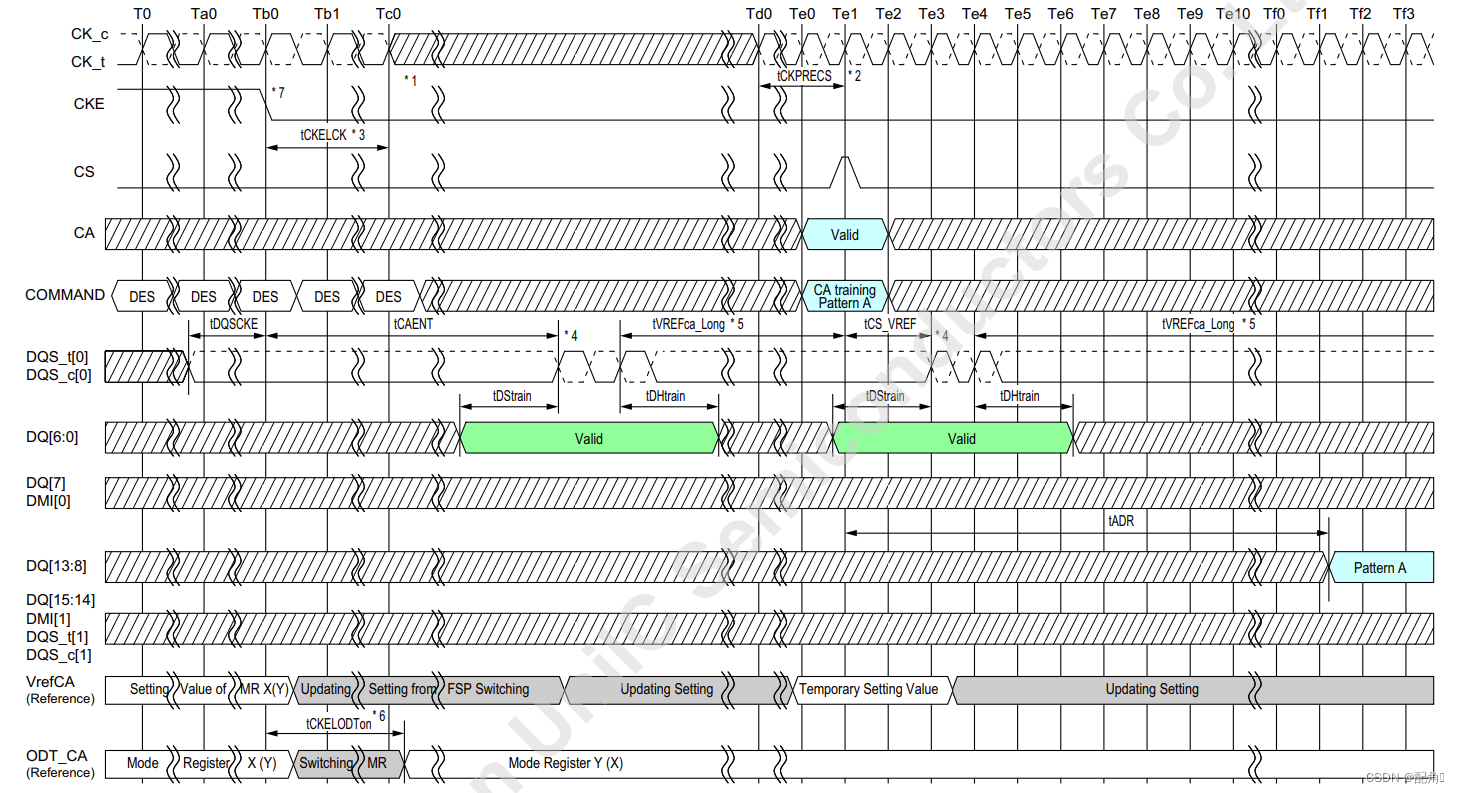

根据时序图,在CKE拉低后必须满足tCKELCK之后,clk可以停止或者切换;在片选拉高之前新的时钟频率必须满足tCKPRECS,在此期间保持CS/CA为低,在接收到training pattern之后,即CS拉高之后,频率至少需要保持tCKPSTCS;SDRAM不会以第一个DQS的边沿对DQ[6:0]进行捕获,每个input DQS(DQS[0])需要至少提供两个连续的脉冲才会用来捕获DQ[6:0]。

CA判决电压的更新需要满足tVREFca_Long,在满足一定条件下,只需要满足tVREFca_Short。在CA发送training pattern之后,需要等待tCS_VREF之后才可以设置下一次判决电压的设定。

single-rank CBT sequence:(从默认状态训练高频)

-

设置所有channel的FSP-WR为1(MR13 OP[6]=1)

-

发送MRW命令进入CBT(MR13 OP[0]=1)

-

驱动CKE为低,并且将CK频率改为高频

-

训练(CA判决电压、CS、CA)

-

离开训练,将CK频率改回低频之后,驱动CKE为高,SDRAM会自动恢复训练前状态的寄存器值

-

所有寄存器训练值写入

-

通过MRW去配置FSP-OP为1,并且将CK改变到高频,即进入训练过的、高频的工作状态,在此状态可以进行一些normal操作或者进行其他频点训练。

多rank CBT sequence: (从默认状态训练高频)

-

将所有的channel和rank写寄存器,配置MR13 OP[6]=1

-

读MR0 OP[7],判断哪个rank是terminating的

-

对terminating的rank发送写寄存器命令,进入CBT(MR13 OP[0]=1)

-

将terminating的rank的CKE拉低,将CK改为高频

-

训练(CA判决电压、CS、CA)

-

离开训练,将CK频率改回低频之后,驱动CKE为高,terminating的rank会自动恢复训练前状态的寄存器值

-

对non-terminating的rank发送写寄存器命令,进入CBT(MR13 OP[0]=1)但是要保持CKE为高

-

通过MRW去配置terminating的rank FSP-OP为1,并且将CK改变到高频

-

驱动non-terminating的rank CKE为低

-

训练(CA判决电压、CS、CA)

-

通过MRW去配置terminating的rank FSP-OP为0

-

离开训练,将CK频率改回低频之后,驱动CKE为高,non-terminating的rank会自动恢复训练前状态的寄存器值

-

所有寄存器训练值写入

-

通过MRW去配置FSP-OP为1,并且将CK改变到高频,即进入训练过的、高频的工作状态,在此状态可以进行一些normal操作或者进行其他频点训练。

四、DQ Training

01 RD DQ Training

执行RD DQ校准的程序是:

-

发出MRW命令以写入MR32(前八位)、MR40(后八位)和MR15(八位)

字节0的反转掩码)和MR20(字节1的8位反转掩码)。

-

可选地,可以跳过此步骤以使用默认模式

-

MR32默认值=5Ah

-

MR40默认值=3Ch

-

MR15默认值=55h

-

MR20默认值=55h

-

发出MPC-1[RD DQ Calibration](RD DQ校准)命令,然后立即发出CAS-2命令。

-

每次收到MPC-1[RD DQ Calibration]命令,然后是CAS-2时

LPDDR4 SDRAM,16位数据突发将在当前设置的RL之后驱动8位

在MR32中编程,然后在所有I/O引脚上在MR40中编程8位。

-

I/O引脚的数据模式将反转,并在相应的反转中编程“1”

掩码模式寄存器位(见表140)。

-

请注意,该模式是在DMI引脚上驱动的,但没有启用数据总线反转功能,即使

如果DRAM模式寄存器中启用了读取DBI。

-

MPC-1[RD DQ校准]命令可以在每个tCCD上无缝发出,tRTRRD

阵列读取命令和MPC-1[RD DQ校准]命令之间需要延迟

以及MPC-1[RD DQ校准]命令和阵列读取之间所需的延迟。

-

通过CAS-2命令接收的操作数必须被驱动为LOW。

-

在刷新期间或SREF期间,可以在任何或没有银行活动的情况下进行DQ读取培训

CKE值较高。

02 DQS-DQ Training

五、Write Training

【DRAM存储器三十八】LPDDR4/DDR4的时序训练相关内容之写方向的训练_lpddr4 vref的作用-CSDN博客

01 Write Leveling

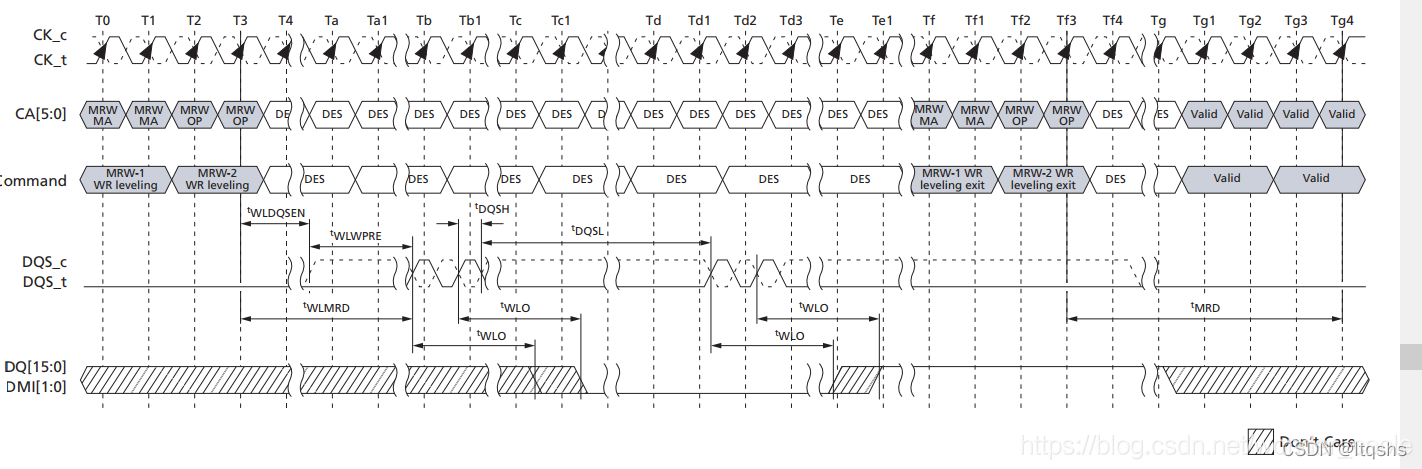

Write Leveling的基本过程是,DDR进入Write Leveling后,用DQS的上升沿采样CLK信号的状态,然后将采样结果通过DQ pin 反馈给MC,MC根据收到的反馈结果后调整CLK-to-DQS的关系,将这个过程不断重复,直到training成功。

LPDDR4的DQ[7:0]传输DQS[0]的反馈结果,DQ[8:15]传输DQS[1]反馈结果。也就是说LPDDR4的两个channel要独立的做Write Leveling,每个channel的16比特也要分两个byte lane来做。

MC通过配置LPDDR4的模式寄存器MR2的OP[7]为1,来让LPDDR4进入write leveling模式。在该模式下,LPDDR4只允许接受DESLECT命令以及退出该模式的MRW命令。当Write Leveling操作完成后,MC使用MRW命令将MR2的OP[7]置0来使LPDDR4退出write leveling操作。

Write leveling应该在write training(DQS2DQ training)前进行

LPDDR4的Write Leveling的具体过程如下(JESD209-4B的4.31):

-

MC设置MR2-OP[7]使LPDDR4进入Write Leveling模式

-

一旦进入Write leveling模式,在tWLDQSEN时间后,MC必须驱动DQS到低电平

-

在tWLMRD时间后提供第一个DQS信号输入。tWLMRD是和不同的MC有关。

-

由于第一个DQS沿不稳定,所以DRAM或许能抓到第一个DQS沿,也可能抓不到,因此MC每次必须提供两个连续的DQS脉冲。每次由DQS沿采到的时钟电平都会被overwritten掉,DRAM会在tWLO时间后异* 步的通过DQ来反馈给MC。

-

MC参考DRAM提供的反馈结果,来增到或减小DQS_t and/or DQS_C的延时设置。

-

重复第4到第5步,直到合适的DQS_t/DQS_c延时建立。

-

通过设置MR2-OP[7]=0, 退出Write-Leveling模式

LPDDR4的训练(training)和校准(calibration)--Write Leveling(写入均衡)_ddr training过程-CSDN博客

六、Read Training

【DRAM存储器三十九】LPDDR4/DDR4的时序训练相关内容之读方向的训练_ddr4 data 训练-CSDN博客

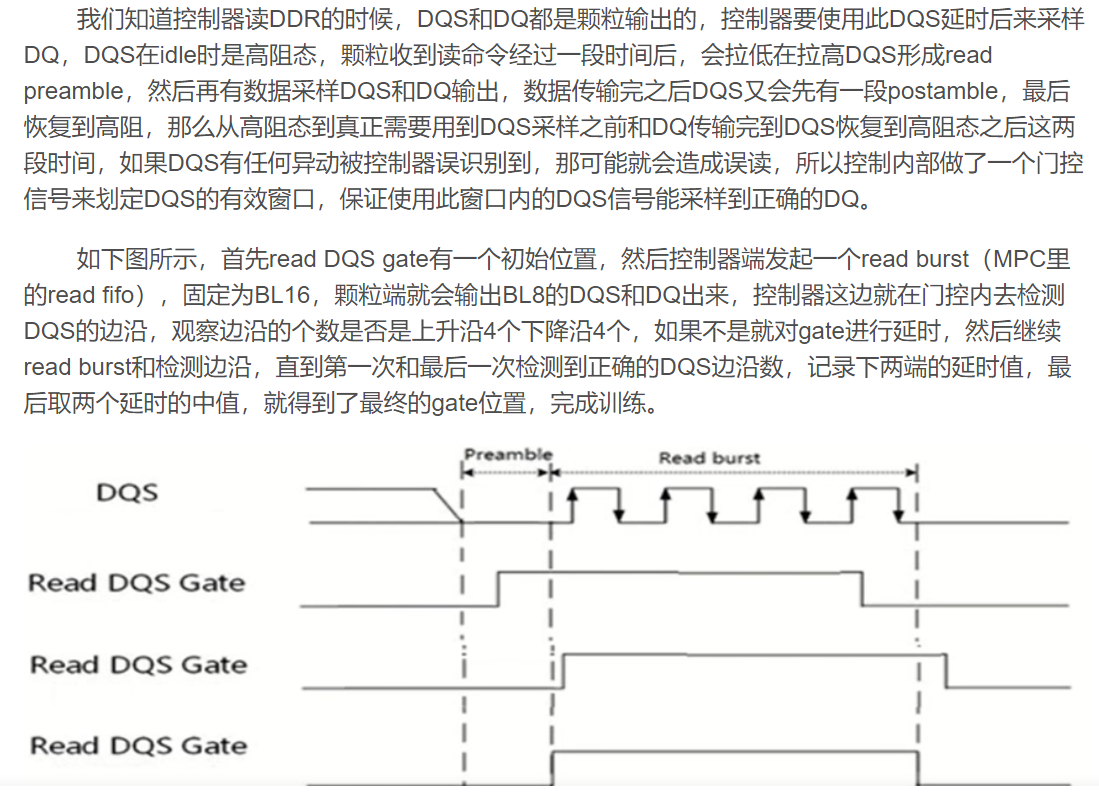

01 Read DQS gate training

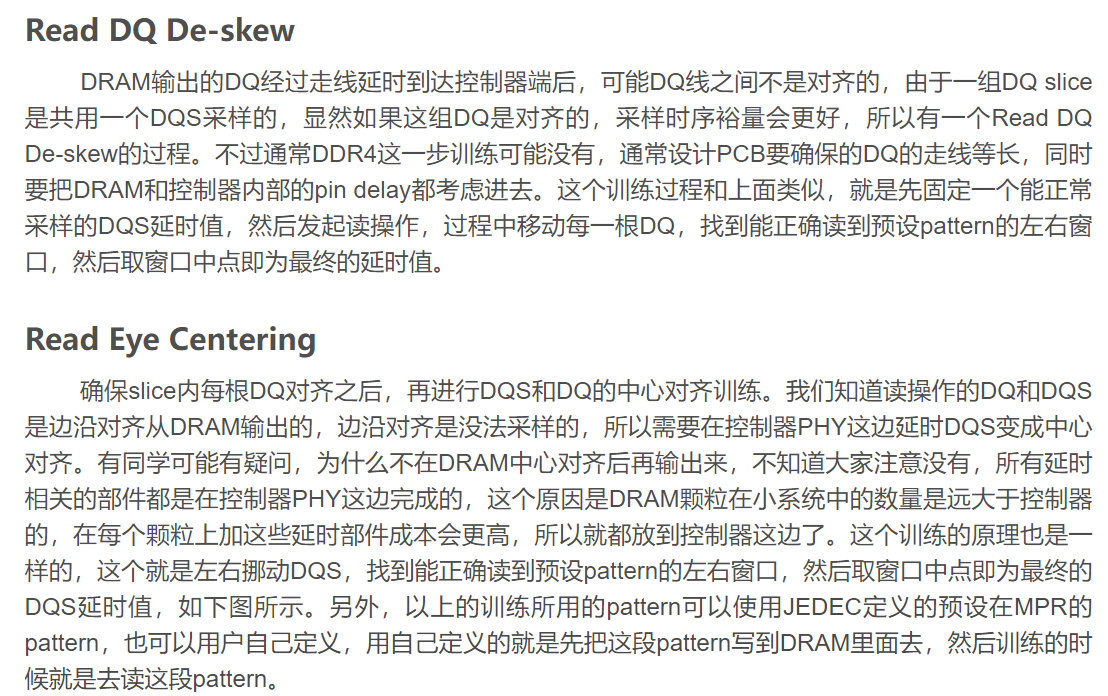

02 Read data eye training

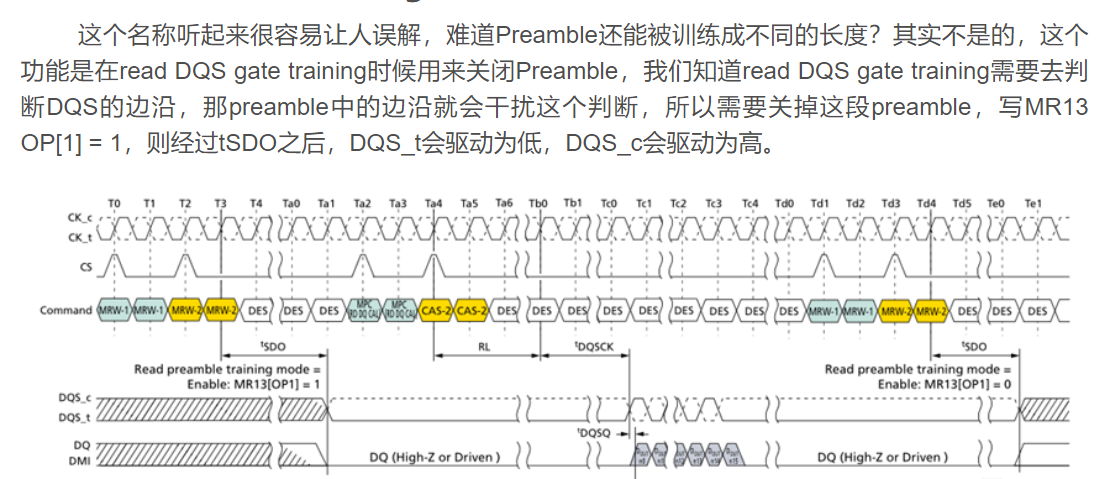

03 Read Preamble training

七、参考文献

DDR4 SDRAM - Initialization, Training and Calibration - systemverilog.io

原文地址:https://blog.csdn.net/qq_41945053/article/details/143807183

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!