数字IC/FPGA——亚稳态及跨时钟域

- 什么是亚稳态

- 亚稳态会造成什么

- 平均故障间隔时间

- 如何解决亚稳态

- 同步时钟和异步时钟

- 单bit电平信号如何跨时钟域

- 单bit脉冲信号如何跨时钟域

- 多bit信号如何跨时钟域

目录

一、亚稳态

1.基本概念

亚稳态是指触发器无法在某个规定时间内达到一个确定的状态,当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时****输出才能稳定在某个正确的电平上。在这个期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

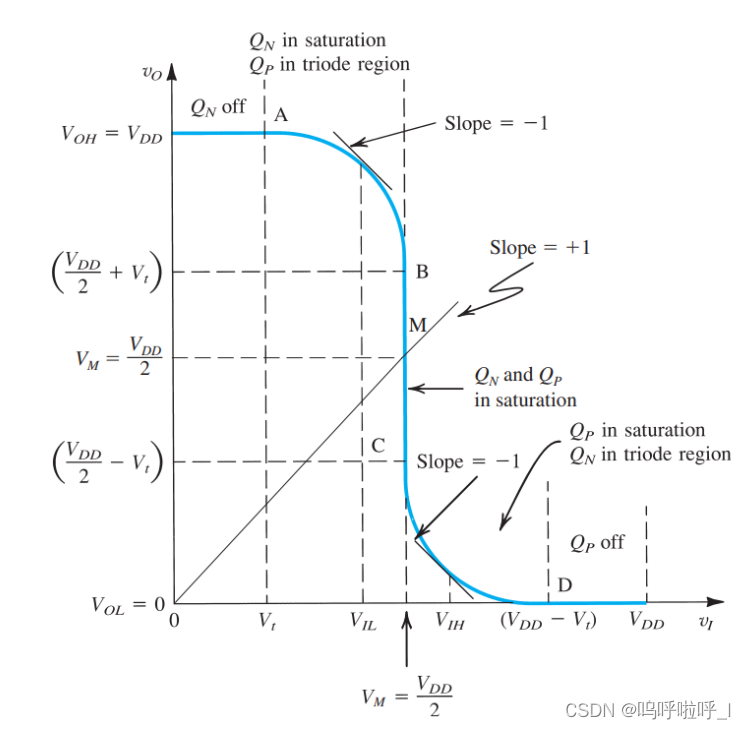

从CMOS层级分析亚稳态产生的原因,下图是一个CMOS反相器的传输特性曲线:

其中BC段为MOS的放大器区,在BC端具有无限大的增益。将输入电压和输出电压相等的点即Vm=VDD/2称作是反相器的阈值电压,电平在这个点附近迅速完成了电平切换。

当输入电压处于0—V_IL时,反相器认为输入为低电平;当输入电压处于V_IH—VDD时,反相器认为输入为高电平。当输入电压处于V_IL—VIH之间时,反相器有可能会将其判断为低电平或高电平中的任意一种。

当输入数据不能够满足寄存器的建立时间和保持时间要求时,采样到的电压就可能会处于上述的V_IL和V_IH之间的区间,就会导致输出处于亚稳态。

2.危害

由于产生亚稳态后,寄存器Q端输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值。在信号传输中产生亚稳态就会导致与其相连其他数字部件将其作出不同的判断,有的判断到“1”有的判断到“0”,有的也进入了亚稳态,数字部件就会逻辑混乱。

3.平均故障时间

平均故障时间指的是系统两次发生故障之间系统平均正常工作的时间,他是系统发生故障概率的倒数。用MTBF表示。平均故障间隔时间越长,系统越可靠。

M T B F = e t M E T / C 2 C 1 ⋅ f C L K ⋅ f D A T A MTBF=\frac{e^{t_{MET}}/C_2}{C_1\cdot f_{CLK}\cdot f_{DATA}} MTBF=C1⋅fCLK⋅fDATAetMET/C2

t_MET代表寄存器从时钟上升沿触发后的时序余量时间;

C1、C2与器件有关的参数,器件的建立时间和保持时间越小,C2越小

f_DATA是数据的变化频率

f_CLK是接收时钟域的时钟频率

4.解决亚稳态的方法

亚稳态不能消除,只能降低其发生的概率。

我们从MTBF入手:当数据的变化频率和接收时钟域的时钟频率越低,C2越小,MTBF越大。

因此可有以下几种方法:

(1)降低时钟频率;

(2)采用反应更快的触发器;

(3)跨时钟域处理。

二、跨时钟域

1.同步电路和异步电路

(1)同步电路

同步电路是指电路中所有由时钟控制的单元,都由一个统一的全局时钟控制。

优点:

①时序收敛;

②可以避免噪声和毛刺的影响(采用的是边沿触发器)

缺点:

时钟偏移的存在会导致时钟树综合时加入缓冲单元,以保证时钟偏移能够维持在一个较小的水平,这样使得电路的面积和功耗增加

(2)异步电路

电路中不是由一个统一的时钟控制,数据传输可以发生在任何时候。

优点:

①由于是异步时钟,无需考虑时钟偏移问题;

②相同条件下比同步电路功耗低;

缺点:

①设计复杂,缺少EDA工具支持;

②很大概率存在竞争与冒险;

③一般无法对异步电路进行静态时序分析。

2.单bit跨时钟域

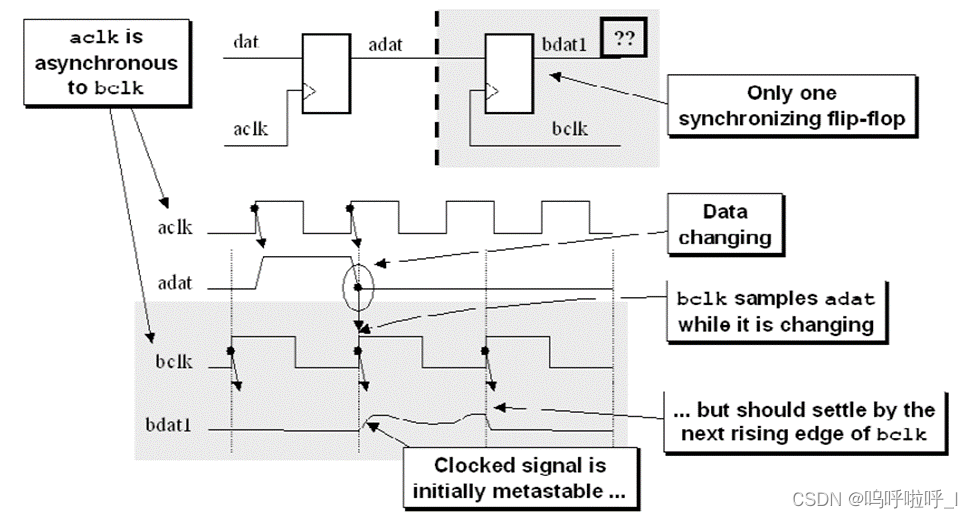

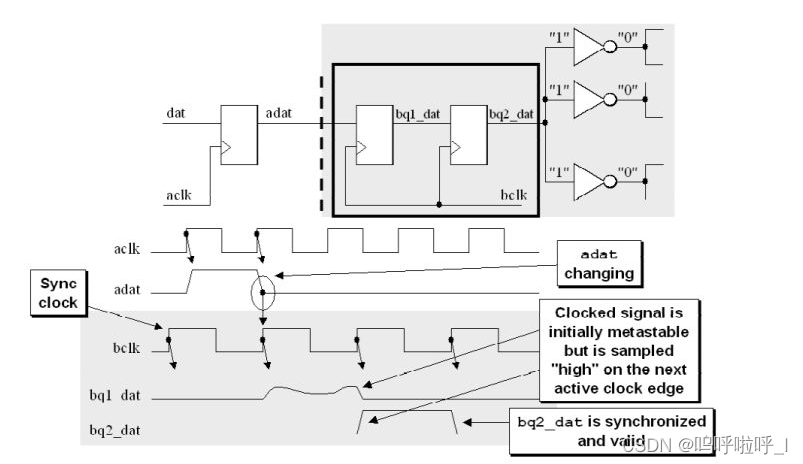

(1)电平信号

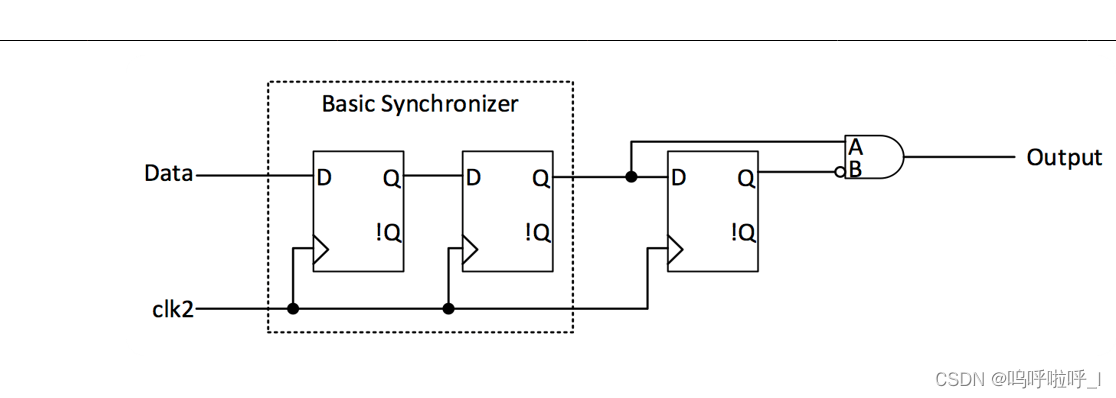

电平信号是指长时间稳定在高电平或低电平的一种信号。因此对其进行跨时钟域处理时,可以直接在接收时钟域对数据进行打拍处理即可,一般为经过两级同步器。

需要注意的是,经过两级同步器并不代表数据采样一定正确,只是可以降低亚稳态发生的概率。

(1)如果亚稳态维持的时间不止一个周期,在下一个时钟上升沿没有稳定,那么第二级的FF也会进入亚稳态,这种情况的概率是1/MTBF

(2)第一级亚稳态在下一个时钟上升沿稳定,但是被是识别为0,那么第二级的FF输出bq2_dat就是0,说明信号跨时钟采样失败。但是这种情况不会造成亚稳态的传播,也就是不会影响后面的设计。针对这种情况,一般会改变设计,不会让快时钟域的单周期脉冲,跨时钟到慢的时钟内采样。

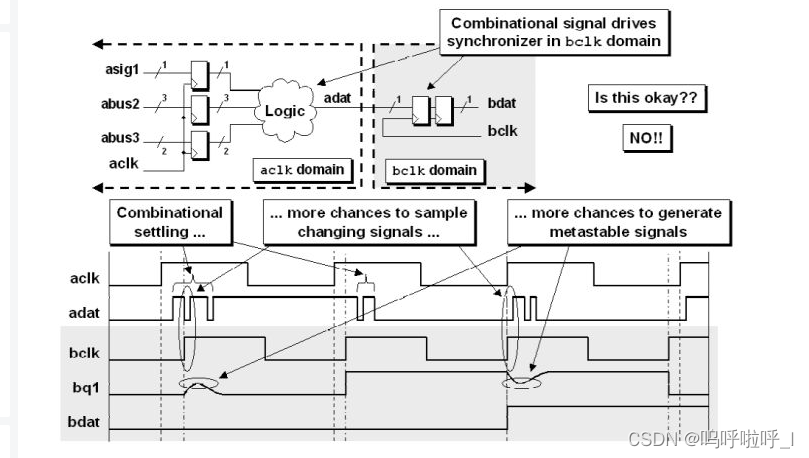

为什么跨时钟信号必须是寄存器的输出,中间不能有组合逻辑?

参考下面这篇文章,写的非常好。

观察图中我们可以发现,当采用组合逻辑后,会出现adat在一个周期内出现了多次跳变,也就是说数据变化的频率变大了,而参考MTBF的公式,当数据频率变大时会导致平均故障间隔时间变小,因此会提高亚稳态发生的概率。

(2)脉冲信号

脉冲信号是指在源时钟下只保持一个时钟周期的信号,为保持其信号特性,跨时钟后该信号需要在目的时钟域下也只保持一个时钟周期。需要考虑原时钟和目的时钟的频率关系,并在设计中采取不同的方式。

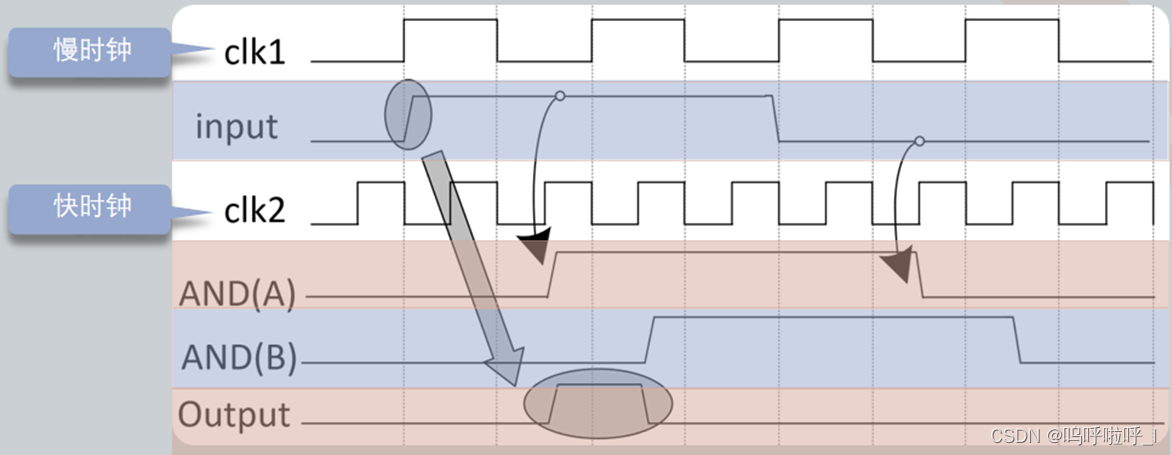

①慢时钟域到快时钟域

直接进行采样可能导致目的时钟对脉冲的重复采样。

将采样信号在目的时钟域打两拍稳定数据,再根据额外打一拍之后做边沿采样(与非),产生脉冲。

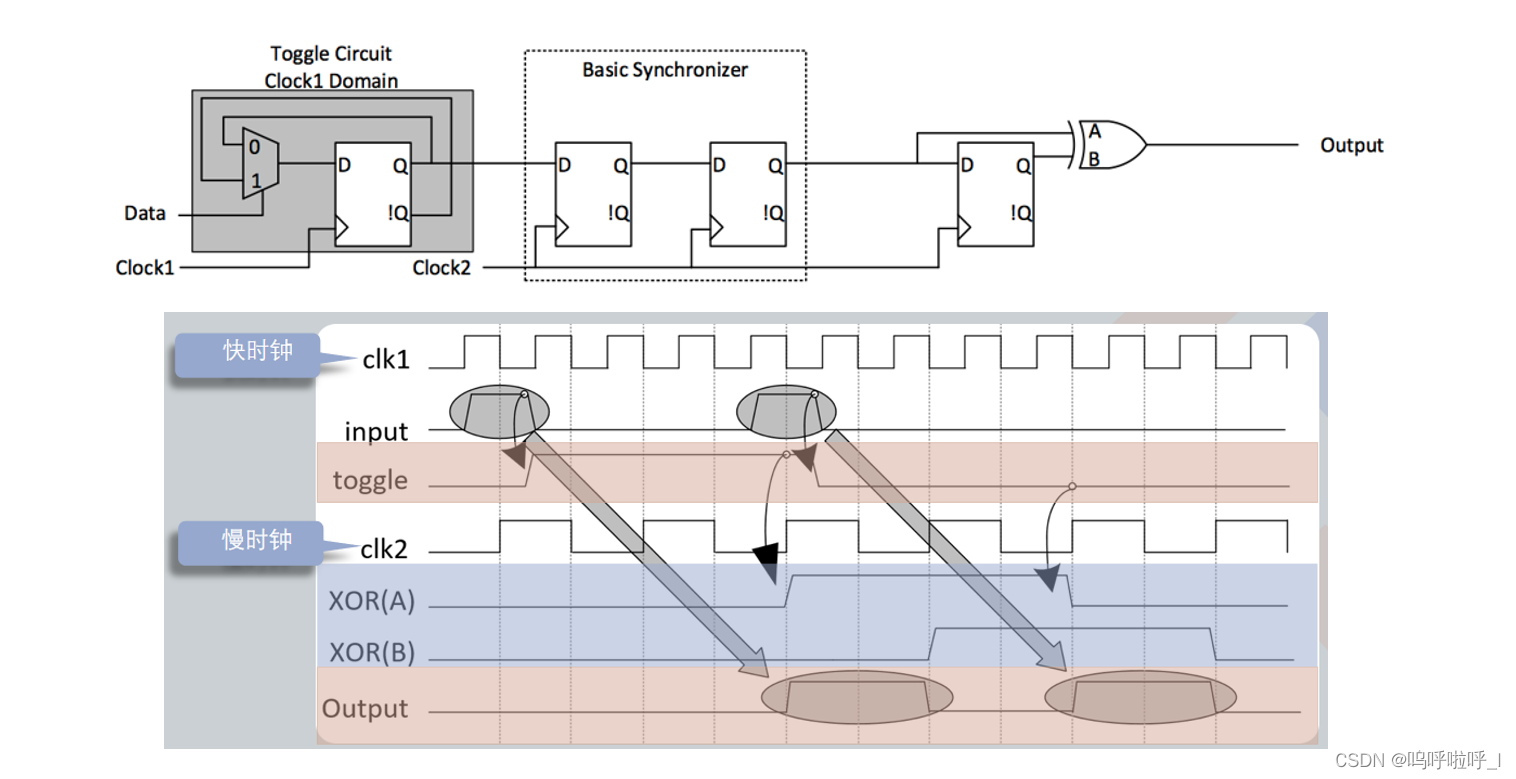

②快时钟域到慢时钟域

这种情况下可能会发生漏采,因此需要先对脉冲信号进行展宽,在源时钟域下根据脉冲信号生成电平信号,检测脉冲信号,将电平信号翻转一次。之后进行两级同步,再提取信号边沿(异或)。

3.多bit跨时钟域

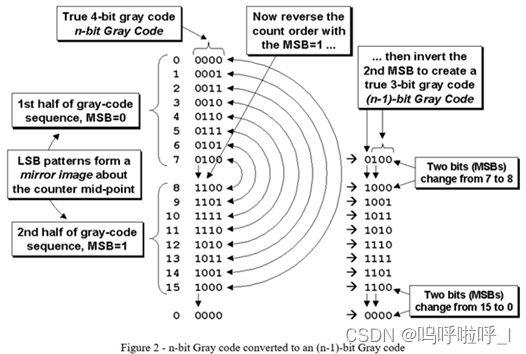

(1)格雷码

格雷码相邻两个数之间只有1bit变化,只要其是连续变化,就可以通过两级同步器进行跨时钟域。

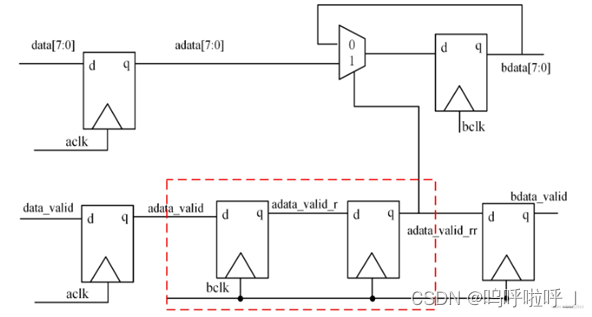

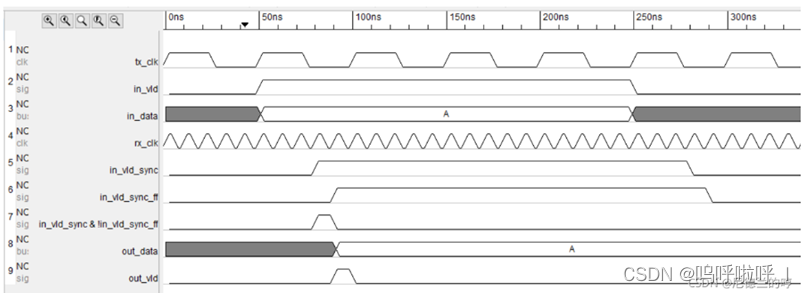

(2)DMUX

对于数值非连续变化、数据保持多拍的多bit信号,可以通过DMUX同步器的方式来进行跨时钟域。

其实现方式为:

对数据有效信号通过两级同步器进行跨时钟域,之后在目的时钟域提取边沿信号,然后再在目的时钟域采样数据信号,因为此时数据信号已经稳定。但是这是对于原时钟域慢目的时钟域快的情况,当原时钟域快目的时钟域慢时需要对有效信号进行展宽,然后跨时钟域。

通常同步器模块的输入和多周期路径规划数据路径需要使用set_false_path命令。因为同步器的输入会出现时序问题。

(3)异步FIFO

对于数值非连续变化并且数据保持一个时钟周期的情况,应使用异步FIFO进行跨时钟域处理。

原文地址:https://blog.csdn.net/qq_43433724/article/details/137718201

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!