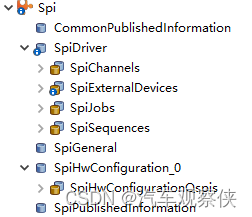

AUTOSAR SPI详解

1.SPI通信

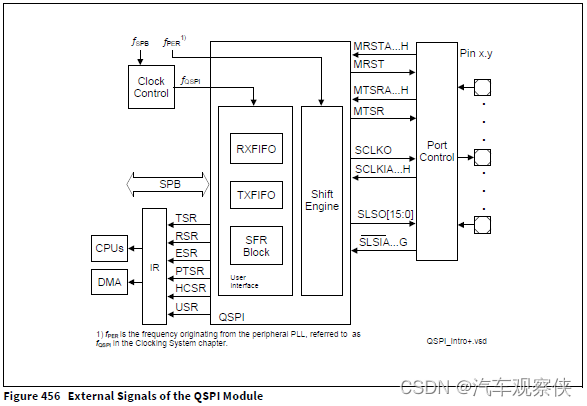

1)SPI通信脚

- SCLO:串行时钟sclk。

- MTSR:主向从方向数据MTSR(主发送从接收)。

- MRST:从向主方向数据MRST(主接收从发送)。

- SLSO:从选择信号SLS,支持16路片选控制。

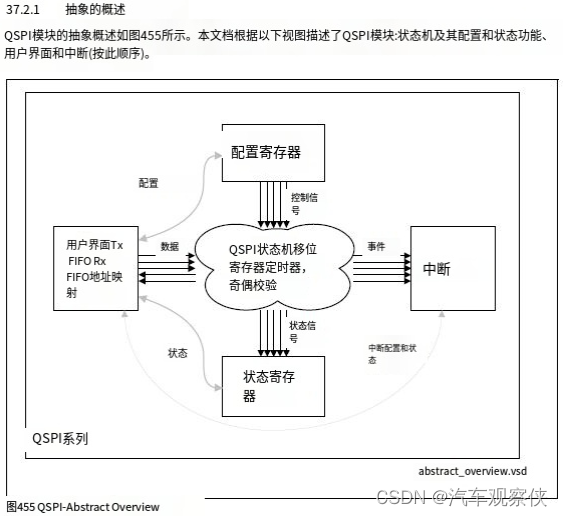

2) SPI状态机

2.SPI通信波形

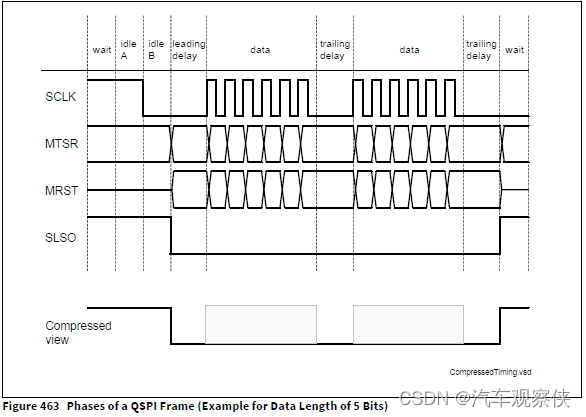

在主机模式,QSPI模块产生定时,串行时钟,和从选择信号。

配置QSPI通信阶段长度的可能性:定时延迟、数据长度、占空比和数据采样。

QSPI帧从激活一个从选择信号SLSO(从空闲到前导延迟阶段)开始,到终止(从拖后延迟到等待或空闲阶段)。它是一个由五个阶段组成的序列:空闲延迟、前导延迟、数据阶段、结束延迟和一个可选的等待阶段。IDLE阶段细分为两个长度相等的阶段:IDLE A和IDLE B。

WAIT:等待阶段只是一个循环,等待Tx FIFO,没有预定义的持续时间,也没有定义位域。

IDLE:空闲延迟,IDLE位域定义了两个长度相同的子阶段IDLEA和IDLEB。

LEAD:前导延迟

DATA:数据段

TRAIL:结束延迟

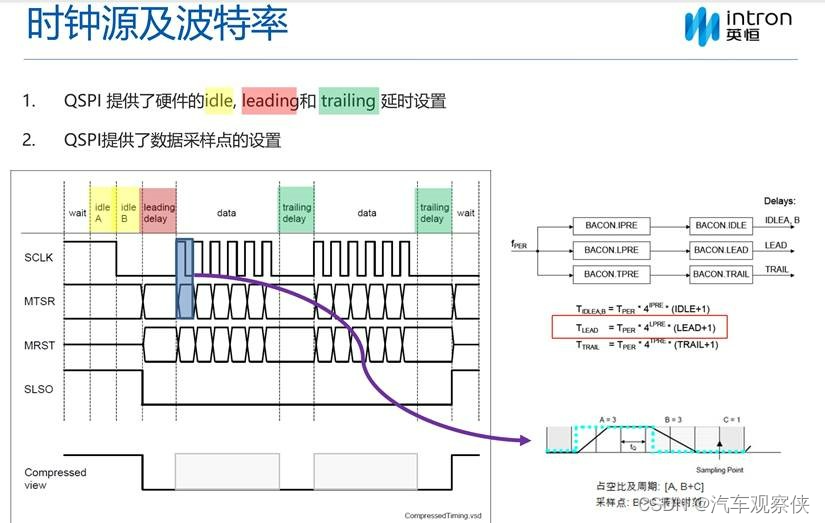

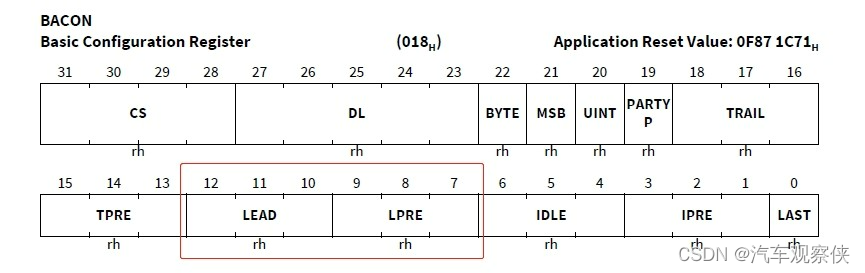

1) 时间延迟

公式里的LPRE和LEAD的值分别对应MCAL的 SpiDelayParamLeadPre 和 SpiDelayParamLeadLength的配置值。

Leading delay 取决于LPRE、LEAD和TPER,如都配置为一样。

可以查看两个模块通道对应的BACON寄存器的实际配置值确认一下。

2) SPI四种时序

SPI模式选择:

CPOL是用来决定SCK时钟信号空闲时的电平,CPHA是用来决定采样时刻的。

CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

CPHA=0,在每个周期的第一个时钟沿采样,CPHA=1,在每个周期的第二个时钟沿采样。

(图片来源于百度百科)

SPI模式设定:主机与从机选择的时钟极性(CPOL)和时钟相位(CPHA)要相同。

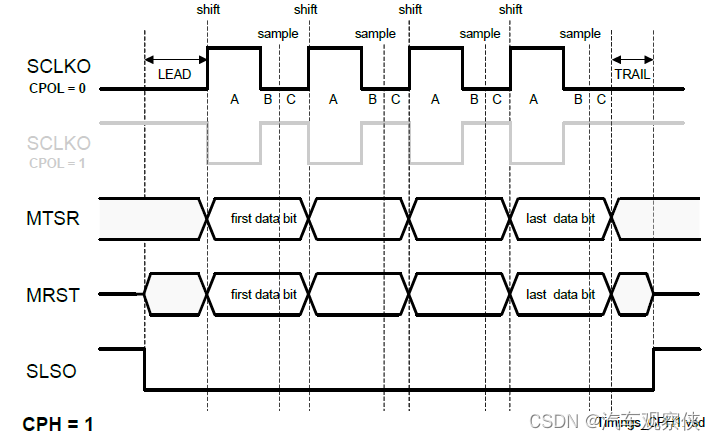

slave通信波形,在SLSO信号选择后立即提供第一个比特的有效值。在这种情况下,使用帧中的第一个时钟边缘锁存第一个比特"first data bit"。第二条边传递第二个比特值,以此类推。帧中的最后一条边传递了一个不在乎的比特。

相位:CPH = 0,CPOL = 1

相位:CPH = 1,CPOL = 1

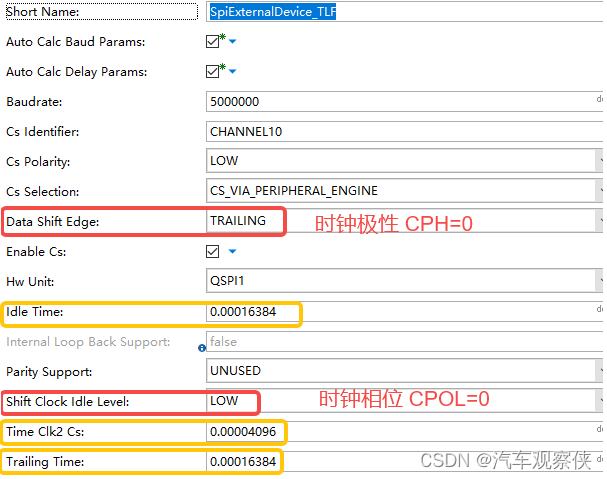

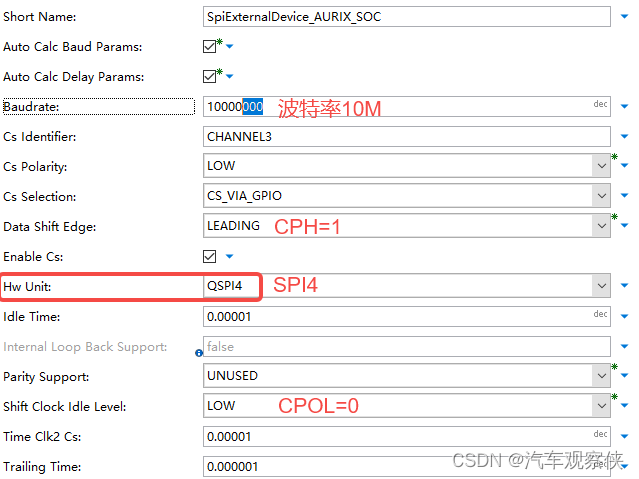

3) 达芬奇配置

(1).配置时钟

SPI模式主机与从机选择的时钟极性(CPOL)和时钟相位(CPHA)要相同。

Data Shift Edge : LEADING / TRAILING

Shift Clock IDLE Level: LOW / HIGH

(2).配置时间延迟

通过修改Idle Time、Time Clk2 Cs、Trailing Time改变通信的整个时间长度。

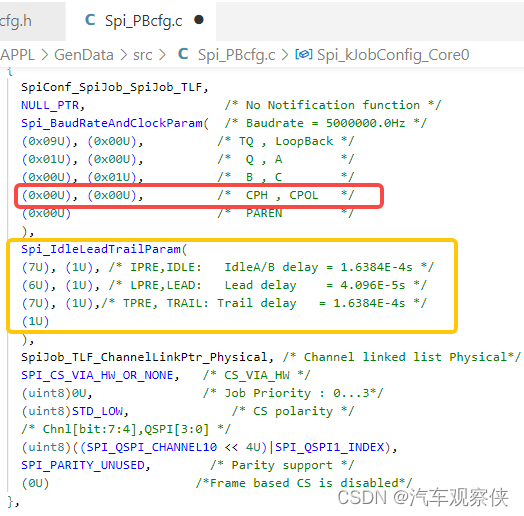

4) 生成代码

3.SPI的一主多从

1)概述

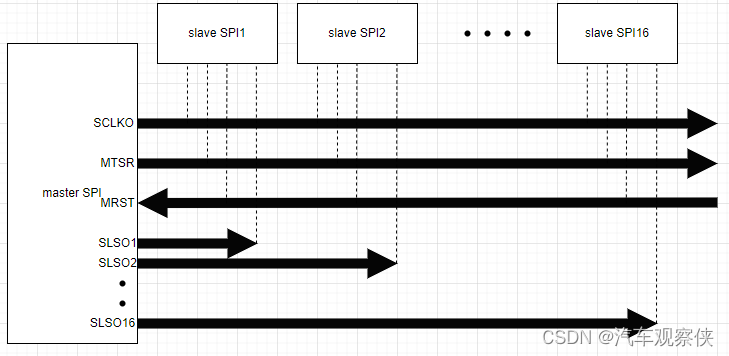

1.AURIX芯片TC3xx的QSPI支持一主与16路从机分别通信,通过片选脚(SLSO)进行切换选择。

2.支持一主分别与时钟极性(CPH)与时钟相位(CPOL)不同的从机分别通信。

3.主从之间配置为异步通信必须使用DMA,同步通信则可以不需要配置DMA。

2)说明

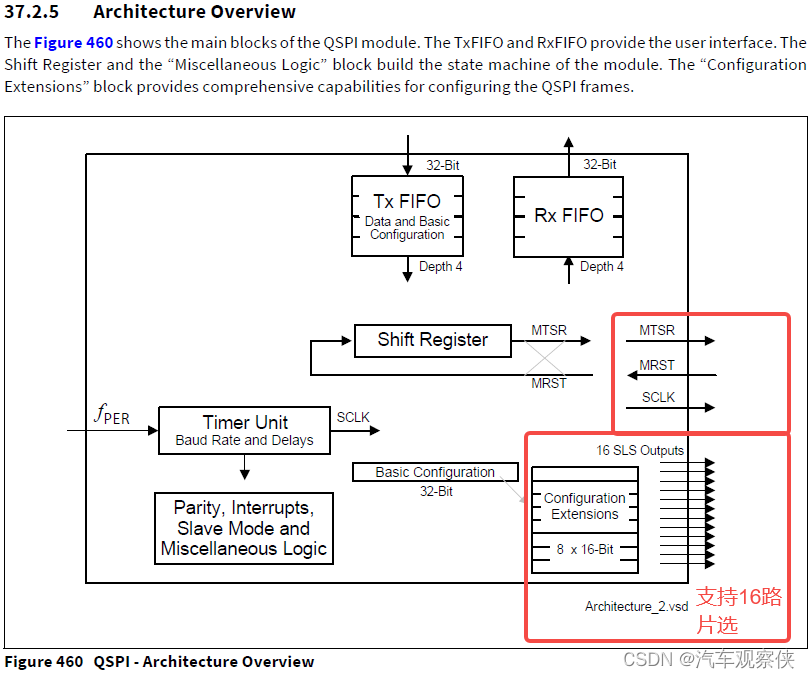

QSPI架构如图所示支持16路片选脚

示意图如下

3)达芬奇配置

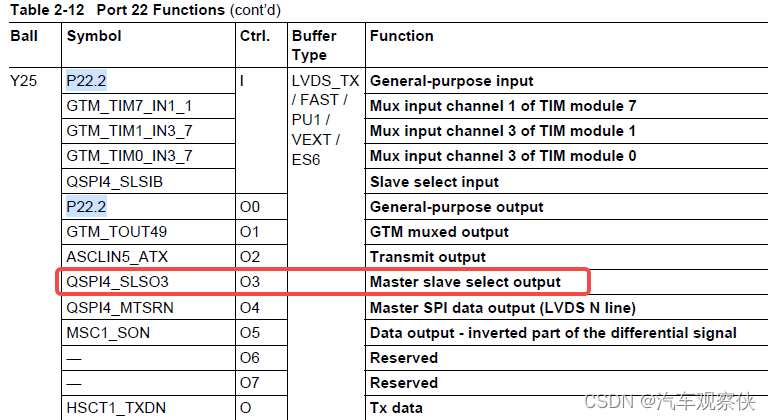

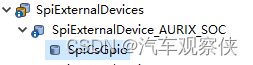

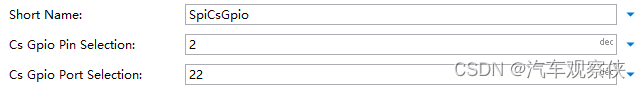

AURIX芯片为主机模式,从机的片选脚连接在P22.2管脚。

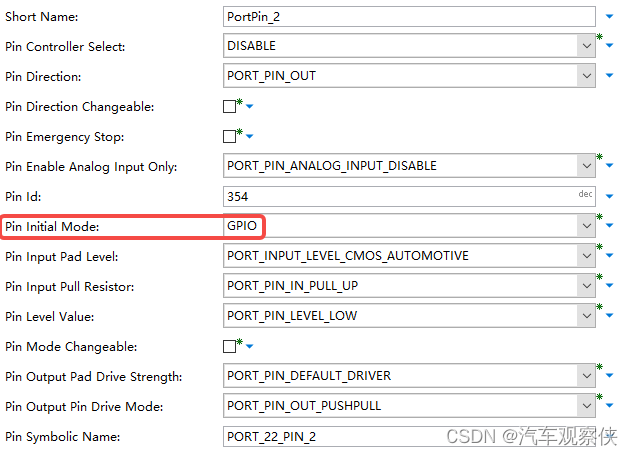

(1)Port口配置为GPIO模式

(2)配置SPI外设驱动

保持主机与从机在同一时钟模式下。

SpiExternalDevices:配置SPI的外设驱动,此处配置主机与外设从机通信参数与SLSO脚选择。

配置主机与外设从机通信参数

选择SLSO脚为P22.2脚

原文地址:https://blog.csdn.net/qq_29986979/article/details/136383852

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!