基于VC709构建FPGA开发学习平台(一)-系统时钟与LED

一、时钟

1. 系统时钟

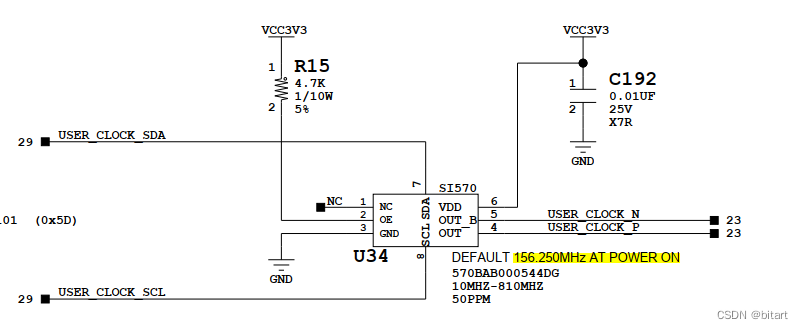

板载U34可编程晶振SI570,为用户提供基础时钟,上电后,默认时钟频率为156.25Mhz,可作为free run时钟源,输入到PLL中,生成系统时钟:

约束为:

set_property PACKAGE_PIN AK34 [get_ports FPGA_CLKIN_156_25_P]

#set_property PACKAGE_PIN AL34 [get_ports FPGA_CLKIN_156_25_N]

set_property IOSTANDARD LVDS [get_ports FPGA_CLKIN_156_25_P]

#set_property IOSTANDARD LVDS [get_ports FPGA_CLKIN_156_25_N]引入到PLL,生成50MHz、100Mhz、200MHz等系统时钟:

mmcm_sysclk A1_mmcm_sysclk (

.clk_in1_p ( FPGA_CLKIN_P ),

.clk_in1_n ( FPGA_CLKIN_N ),

.clk_out1 ( sys_clk ),

.clk_out2 ( sys_clk_50m ),

.clk_out3 ( sys_clk_200m ),

.locked ( sys_locked )

); 2. SMA时钟

板卡上J31和J32 SMA连接器直接连接在FPGA的MRCC管脚,用作时钟输入时,可以替代系统时钟作为FPGA的时钟源;用作输出时,可将FPGA的时钟输出至片外用于测试或其他目的。

# SMA CLOCK

set_property PACKAGE_PIN AJ32 [get_ports SMA_out_p]

set_property IOSTANDARD LVDS [get_ports SMA_out_p]

作为输出时,使用方法为:

....

output wire SMA_out_p,

output wire SMA_out_n,

....

// 将sys_clk引出到同轴连接器进行测试

wire sys_clk ;

mmcm_sysclk A1_mmcm_sysclk (

.clk_in1_p ( FPGA_CLKIN_P ),

.clk_in1_n ( FPGA_CLKIN_N ),

.clk_out1 ( sys_clk ),

.clk_out2 ( sys_clk_50m ),

.clk_out3 ( sys_clk_200m ),

.locked ( sys_locked )

);

wire sys_clk_ddr;

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_out_clock_si5324 (

.Q(sys_clk_ddr), // 1-bit DDR output

.C(sys_clk ), // 1-bit clock input

.CE(1'b1), // 1-bit clock enable input

.D1(1'b1), // 1-bit data input (positive edge)

.D2(1'b0), // 1-bit data input (negative edge)

.R(), // 1-bit reset

.S() // 1-bit set

);

OBUFDS #(

.IOSTANDARD("DEFAULT"), // Specify the output I/O standard

.SLEW("SLOW") // Specify the output slew rate

) OBUFDS_inst_si5324 (

.O (SMA_out_p), // Diff_p output (connect directly to top-level port)

.OB(SMA_out_n), // Diff_n output (connect directly to top-level port)

.I (sys_clk_ddr) // Buffer input

);3. DDR时钟

板卡包含两组DDR,每一组DDR提供了一个200MHz的参考时钟,在生成MIG时,直接指定引脚即可。

二、用户LED

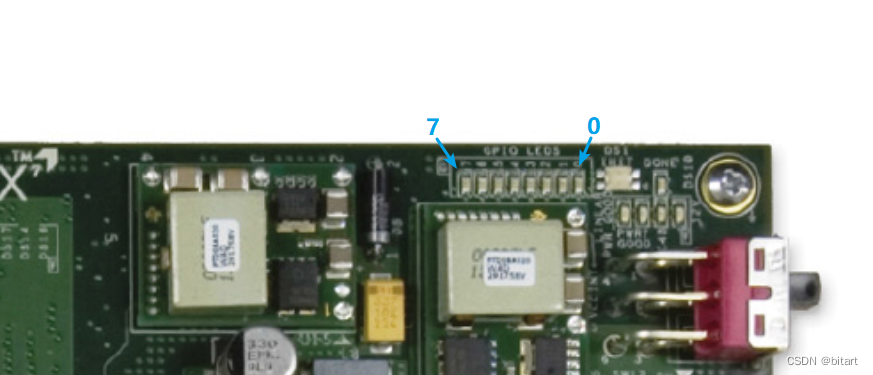

板卡具有8个用户LED,位于板卡右上角,从右至左分别为LED0~LED7:

位置约束为:

set_property PACKAGE_PIN AM39 [get_ports BOARD_LED0]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED0]

set_property PACKAGE_PIN AN39 [get_ports BOARD_LED1]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED1]

set_property PACKAGE_PIN AR37 [get_ports BOARD_LED2]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED2]

set_property PACKAGE_PIN AT37 [get_ports BOARD_LED3]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED3]

set_property PACKAGE_PIN AR35 [get_ports BOARD_LED4]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED4]

set_property PACKAGE_PIN AP41 [get_ports BOARD_LED5]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED5]

set_property PACKAGE_PIN AP42 [get_ports BOARD_LED6]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED6]

set_property PACKAGE_PIN AU39 [get_ports BOARD_LED7]

set_property IOSTANDARD LVCMOS18 [get_ports BOARD_LED7]

原文地址:https://blog.csdn.net/bitart/article/details/137588521

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!