PotatoPie 4.0 实验教程(26) —— FPGA实现摄像头图像拉普拉斯锐化

为什么要对图像进行拉普拉斯锐化

对图像进行拉普拉斯锐化的目的是增强图像的边缘和细节,使图像看起来更加清晰和锐利。这种技术常用于图像处理中,具体原因如下:

-

增强图像的边缘信息:拉普拉斯锐化可以突出图像中的边缘特征,使得边缘更加清晰和突出。它通过对图像进行高通滤波来增强高频信息,从而使得图像中的边缘更加明显。

-

提高图像的对比度:拉普拉斯锐化可以增强图像的对比度,使得图像中的灰度变化更加明显。这有助于改善图像的视觉效果,使得图像更加生动和逼真。

-

减少图像模糊:拉普拉斯锐化可以减少图像的模糊效果,使得图像看起来更加清晰和细致。它可以去除图像中的低频成分,从而提高图像的清晰度。

-

增强图像的细节:拉普拉斯锐化可以增强图像中的细节信息,使得图像中的纹理和细微的特征更加明显。这对于图像分析、目标检测和识别等任务非常有帮助。

-

图像预处理:拉普拉斯锐化通常作为图像预处理的一部分,用于改善后续图像处理算法的性能和准确性。例如,在图像识别、目标跟踪和计算机视觉任务中,对图像进行拉普拉斯锐化可以提高算法的鲁棒性和准确率。

总的来说,拉普拉斯锐化是一种常用的图像增强技术,可以提高图像的质量和可用性,使得图像在各种应用领域中都能取得更好的效果。

拉普拉斯锐化算法步骤

图像的拉普拉斯锐化是根据图像每个像素领域内的像素到该像素的突变程度来计算的,计算的是图像像素的变化程度。我们知道,一阶微分函数描述了函数图像是朝哪个方向变化的,或增长或降低。二阶微分函数描述的则是图像变化的速度,是急剧增长(下降)还是平缓的增长(下降)。根据上述的描述,可以知道二阶微分可以得到图像色彩的过渡程度,比如白色与黑色的过渡。

换句话说,当邻域中心像素灰度低于它所在的领域内其它像素的平均灰度时,此中心像素的灰度应被进一步降低;当邻域中心像素灰度高于它所在的邻域内其它像素的平均灰度时,此中心像素的灰度应被进一步提高,以此实现图像的锐化处理。

对于3×3的拉普拉斯锐化算子,一个常见的模板如下:

0 -1 0-1 4 -10 -1 0

这个3×3的模板是最常用的拉普拉斯锐化算子之一,中心像素的权重是4,周围的4个像素的权重是-1。这个模板可以突出图像中的边缘和细节,增强图像的锐度。这个卷积核涵盖了图像周围的8个像素,包括水平、垂直和对角方向。通过应用这个卷积核,可以突出图像中的边缘和纹理特征,实现图像的增强和锐化处理。

该卷积核对图像进行二阶微分运算,突出了图像中灰度的快速变化,从而增强了图像的边缘和细节。在卷积之后,可以将得到的图像与原始图像相加,或者将得到的图像与原始图像进行混合,以实现拉普拉斯锐化效果。拉普拉斯锐化可以使图像的边缘更加清晰,细节更加突出,但如果处理不当,可能会导致图像中出现噪点或者增强图像中的噪点。因此,在应用拉普拉斯锐化技术时,需要谨慎调整参数,以获得最佳的图像增强效果。

我们FPGA工程中使用的算子是

0 -1 0-1 5 -10 -1 0

为了使边缘更加锐利,我们将拉普拉斯滤波器的中心值从4更改为5时。这会导致输出图像边缘的增强效果更明显,因为增加中心像素的权重,使其对输出像素的贡献更大,但也可能导致图像中的噪声被放大。

当应用拉普拉斯锐化算法时,通常需要以下步骤:

-

图像平滑化:首先,应用高斯滤波器或其他平滑滤波器对原始图像进行平滑化处理。平滑化可以减少图像中的噪声,并有助于提取图像的细节。

-

计算拉普拉斯算子:接下来,通过应用预定义的拉普拉斯算子(也称为拉普拉斯核)来计算图像的拉普拉斯变换。这个算子可以突出图像中的边缘和细节,通过检测像素值的变化来增强图像的锐度。

-

图像叠加:将原始图像与拉普拉斯变换的结果进行叠加,以增强图像的边缘和细节。这通常是通过将原始图像的像素值与拉普拉斯变换的像素值相加来实现的。这个过程可以突出图像中的边缘和细节,使图像看起来更加清晰和锐利。

-

调整亮度:由于拉普拉斯变换可能导致图像的像素值超出了合适的范围,因此在叠加后的图像中可能会出现亮度失真。为了解决这个问题,通常需要对图像的亮度进行调整,以确保像素值在合适的范围内。这可以通过灰度拉伸或直方图均衡等技术来实现。

-

结果输出:最后,处理后的图像可以保存为图像文件或直接显示在屏幕上,以供后续分析或应用。这样处理后的图像通常具有更好的边缘和细节,看起来更加清晰和锐利,适用于各种计算机视觉应用。

pyton代码实现上述过程

python代码如下:

PotatoPie 4.0 实验教程(26) —— FPGA实现摄像头图像拉普拉斯锐化-Anlogic-安路论坛-FPGA CPLD-ChipDebug

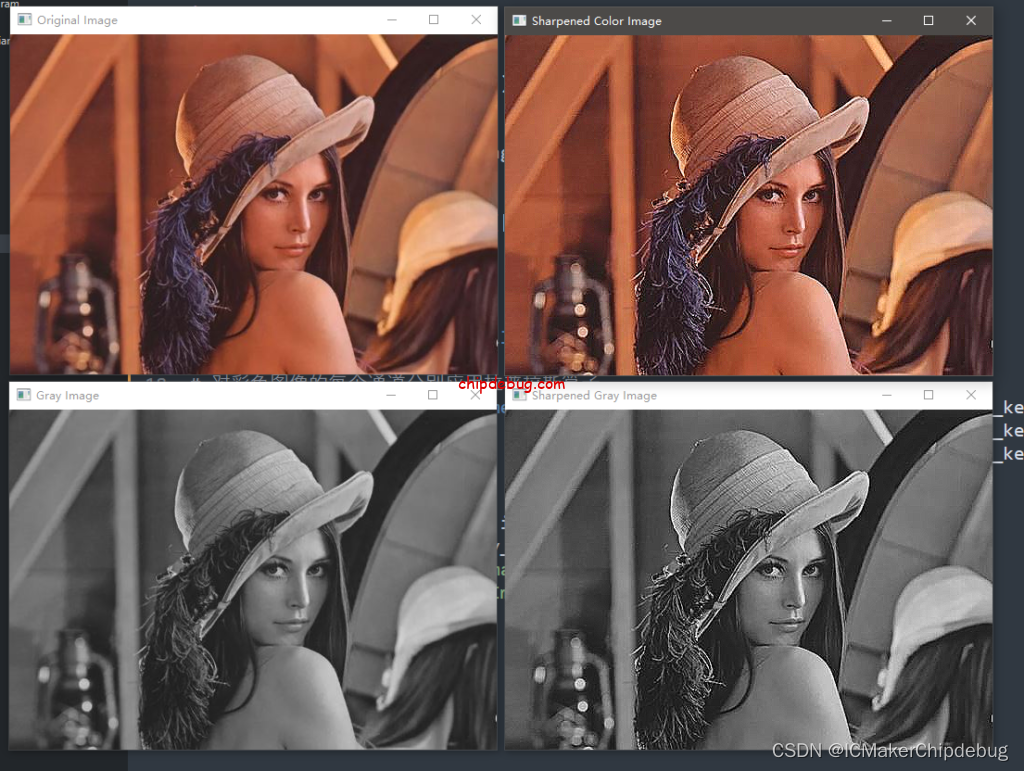

在这个示例中,首先读取彩色图像,然后将其转换为灰度图像。然后,对灰度图像应用拉普拉斯算子得到锐化后的灰度图像。对于彩色图像,分别对其三个通道应用拉普拉斯算子,然后将结果合并成彩色图像。最后,显示原始图像、灰度图像、锐化后的灰度图像和锐化后的彩色图像。

matlab实现图像拉普拉斯锐化

PotatoPie 4.0 实验教程(26) —— FPGA实现摄像头图像拉普拉斯锐化-Anlogic-安路论坛-FPGA CPLD-ChipDebug

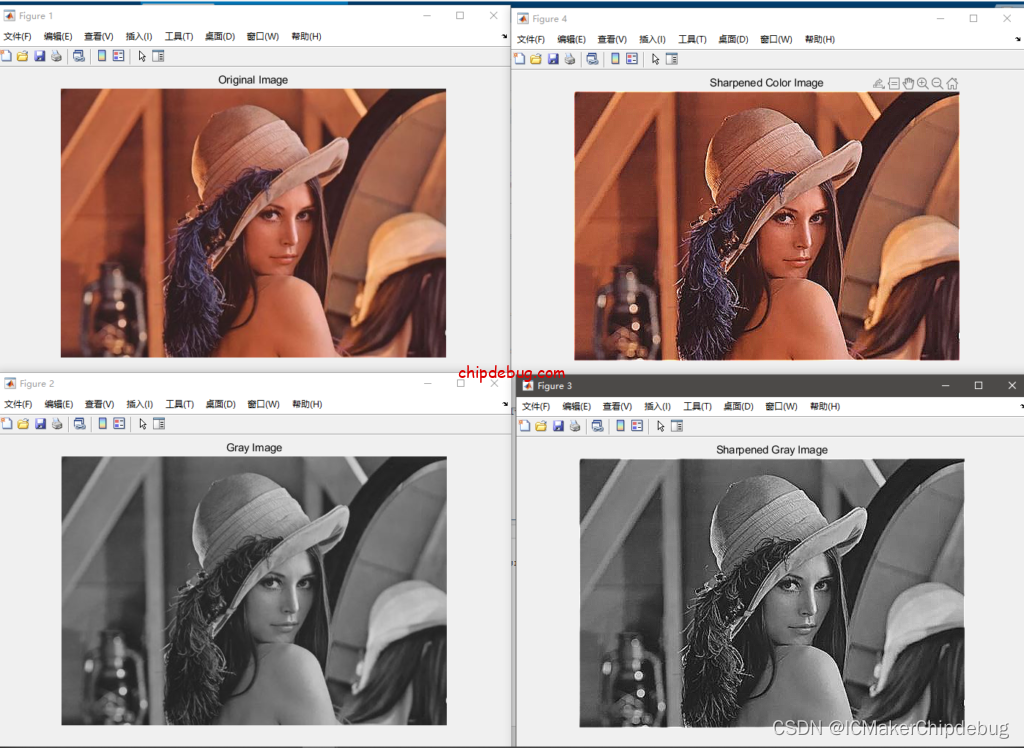

这段 MATLAB 代码实现了图像的锐化功能,具体功能说明如下:

-

img_sharpen函数定义了整个处理过程,包括读取彩色图像、转换为灰度图像、应用拉普拉斯算子进行图像锐化,并显示原始图像、灰度图像和锐化后的图像。 -

获取当前脚本所在目录,以便读取图像文件。

-

读取彩色图像

Lena.jpg。 -

使用

rgb2gray函数将彩色图像转换为灰度图像。 -

定义拉普拉斯锐化算子

laplacian_kernel,用于图像锐化。 -

对灰度图像应用拉普拉斯算子,使用

imfilter函数进行卷积运算,得到锐化后的灰度图像sharpened_gray_image。 -

对彩色图像的每个通道分别应用拉普拉斯算子,同样使用

imfilter函数,得到锐化后的彩色图像sharpened_color_image。 -

分别显示原始图像、灰度图像和锐化后的图像,使用

imshow函数,并设置标题。

通过这段代码,可以清晰地展示图像的锐化效果,有助于突出图像中的细节和边缘特征。

FPGA工程分析

工程层次图

与demo18相比,只是多了一个img_laplacian_fltr的模块,也就是下面这一段代码,在从SDRAM读出来之后,经它处理后再输出hdmi_tx模块。

img_laplacian_fltr

(

.i_clk(clk_pixel),

.i_rst_n(sys_rst_n),

.i_hs(VGA_HS),

.i_vs(VGA_VS),

.i_en(VGA_DE),

.i_r(VGA_RGB[23:16]),

.i_g(VGA_RGB[15:8] ),

.i_b(VGA_RGB[7:0] ),

.o_hs(laplacian_hs),

.o_vs(laplacian_vs),

.o_en(laplacian_de),

.o_r(laplacian_data[23:16]),

.o_g(laplacian_data[15:8] ),

.o_b(laplacian_data[7:0] )

);img_laplacian_fltr模块代码分析

考虑到FPGA示例的简洁性,我们的FPGA示例工程仅进行第二步计算拉普拉斯算子处理后便显示,不做与彩色原图的合并处理。

img_laplacian_fltr img_buf fifo_3line这三个代码模块相互关联,构成了一个图像 Laplacian 滤波器。这里的三个模块的作用分别是:

fifo_3line模块:FIFO 内存队列生成器,用于数据的存储和读取。img_buf模块:用上面的FIFO模块构成行缓存,让图像的像素按3*3进输。

img_laplacian_fltr模块:图像 Laplacian 滤波器模块,对输入图像进行 Laplacian 滤波处理。

img_laplacian_fltr模块里面分别对RGB三个通道进行了拉普拉斯算子的模版运算,并处理了对行场信号进行延时以实现与数据同步。模块主以下几步:

- 首先用

img_buf实现图像的行缓存,R、G、B的每个通道经过缓存之后由原来的每个时钟一个像素变成了每个时钟9个像素,也就是每个时钟输出一个3*3的像素。 - 对每个通首3*3的像素值先进行加法运算然后再进行减法运算(上面的拉普拉斯算子只有这两种运算),最后求和(verilog代码的注释对计算过程以及计算优化作了详细说明,请参见代码)。

- 对求出来的和进行输出范围限定,避免计算出来的值下溢超过0或上溢超过255。

- 同前面的例程一样,需要将行场信号和数据同步,因此将行场信号打一拍。

算法的核心:

0 -1 0-1 5 -10 -1 0

展开就是:

0*pixel11 -1*pixel12 0*piexe13

-1*pixel21 5*pixel22 -1*piexl23

0*pixel31 -1*pixel32 0*pixel33

前面讲过img_buf 会把图像进行缓存,然后每次输出这三行的三列,也就是3*3个像素。上式中pixel11表示第一行一列的像素,同理pixe32表示第三行的第二个像素。

算法的实现及优化详见verilog代码及其注释。

管脚约束

与PotatoPie 4.0 实验教程(18) —— FPGA实现OV5640摄像头采集以SDRAM作为显存进行HDMI输出显示相同,不作赘述。

时序约束

与PotatoPie 4.0 实验教程(18) —— FPGA实现OV5640摄像头采集以SDRAM作为显存进行HDMI输出显示相同,不作赘述。

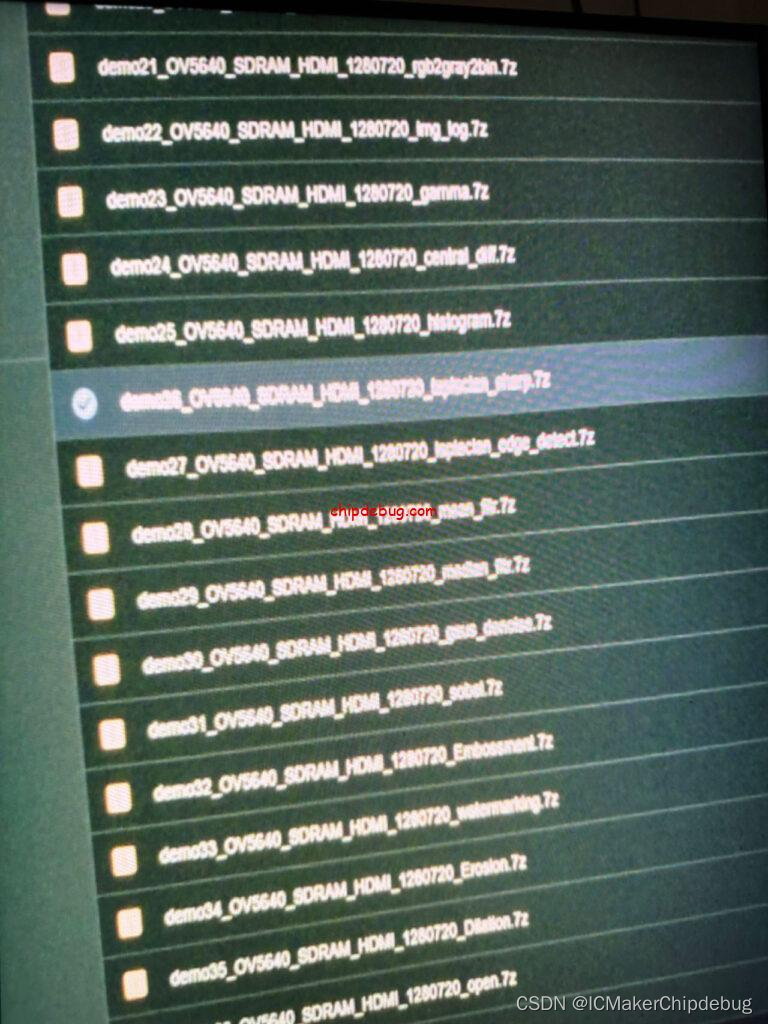

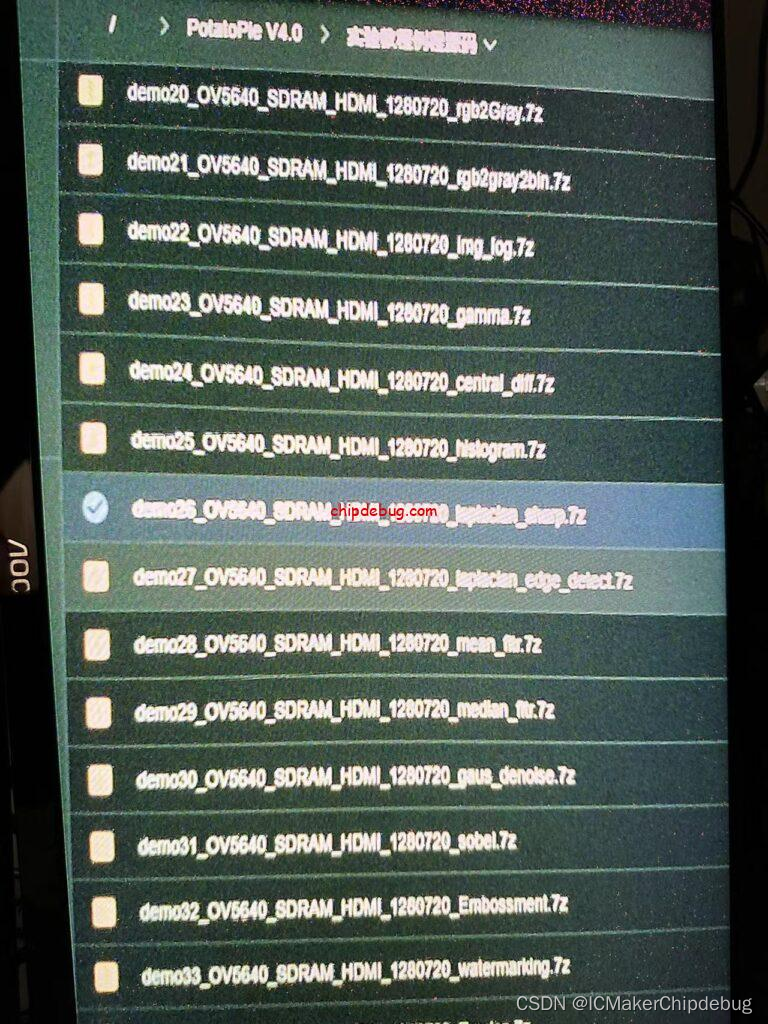

实验结果图

原图

锐化处理后边界是增强了,但噪点也增加了

原文地址:https://blog.csdn.net/ICMakerChipdebug/article/details/138138022

免责声明:本站文章内容转载自网络资源,如本站内容侵犯了原著者的合法权益,可联系本站删除。更多内容请关注自学内容网(zxcms.com)!